## Institut fur Informatik and Praktische Mathematik

Christian-Albrechts-Universitat Kiel

Olshausenstraße 40-60

D - 2300 Kiel 1

Tel. (0431) 880 - 4461

MIMOLA REPORT

Revision 1 and

MIMOLA SOFTWARE SYSTEM USER MANUAL

## CONTENTS

|       |                                          | Page |

|-------|------------------------------------------|------|

| 1.    | INTRODUCTION                             | 1    |

| 2.    | APPLICATIONS                             | 6    |

| 2.1   | Non procedural Description of Hardware   | 6    |

| 2.2   | Functional Description                   | 8    |

| 2.3   | Alcorithmic Description                  | 10   |

| 2.4   | Microprogramming Language                | 13   |

| 3.    | SYNTAX                                   | 1 4  |

| 4. H  | ARDWARE DATA STRUCTURE                   | 18   |

| 4.1   | Group, Module                            | 18   |

| 4.2   | Port, Input                              | 18   |

| 4.3   | Field                                    | 19   |

| 4.4   | Connection                               | 20   |

| 4.5   | Data Structure Entries                   | 20   |

| 5.    | DECLARATION                              | 22   |

| 5.1   | Declaration of Modules, Ports and Fields | 22   |

| 5.1.1 | 1 Addition                               | 22   |

| 5.1.2 | 2 Deletion                               | 26   |

| 5.2   | Standard Modulos                         | 26   |

| 5.2.  | 1 Random Access Memory                   | 26   |

| 5.2.2 | 2 Reqister                               | 27   |

| 5.2.3 | 3 Stack                                  | 27   |

| 5.2.4 | 4 Instruction                            | 28   |

| 5.2.5 | 5 Hardwired Constant                     | 29   |

|       |                            | Page |

|-------|----------------------------|------|

| 5.2.6 | Monadic operator           | 29   |

| 5.2.7 | Dyadic Operator            | 29   |

| 5.2.8 | Triadic Operator           | 30   |

| 5.2.9 | Network                    | 30   |

| 5.3   | Declaration of Connections | 30   |

| 5.3.1 | Addition                   | 30   |

| 5.3.2 | Deletion                   | 31   |

| 5.4   | Data Paths Conventions     | 32   |

| 5.4.1 | Statements                 | 32   |

| 5.4.2 | Destinations               | 33   |

| 5.4.3 | Bit-to-Bit Assignment      | 33   |

| 5.4.4 | Attributes                 | 33   |

| 5.4.5 | Distributors               | 35   |

| 5.4.6 | Concatenation              | 35   |

|       |                            |      |

| 6.    | ASSIGNMENTS                | 37   |

| 6.1   | Identifier Assignment      |      |

| 6.2   | Storage Map Assignment     |      |

| 6.3   | Initial Value Assignment   | 38   |

| 6.4   | Record Assignment          | 38   |

| 6.5   | Example                    | 38   |

| 7.    | PROGRAM                    | 39   |

| 7.1   | Fundamental Semantics      | 39   |

| 7.2   | Labels                     | 40   |

| 7.3   | Functions                  | 41   |

| 7.4   | Identifiers                | 42   |

| 7.5   | Operands                   | 43   |

|       |                            |      |

|                            |                                               | Page     |

|----------------------------|-----------------------------------------------|----------|

| 7.5.1                      | General Features                              | 43       |

| 7.5.2                      | Constants                                     | 43       |

| 7.5.3                      | FOR Loop Control Variable                     | 43       |

| 7.5.4                      | Dummy Source                                  | 44       |

| 7.6 A                      | llocator Conventions                          | 44       |

| 7.6.1                      | Default Replacement of Identifiers, Functions | 44       |

|                            | and Constants                                 |          |

| 7.6.2                      | Duplicates of Operators                       | 45       |

| 7.6.3                      | Port Allocation                               | 46       |

| 7.6.4                      | Default Bitnumbers                            | 47       |

| 7.7                        | High Level Language Elements                  | 48       |

| 8. MAC                     | ROS                                           | 49       |

| 8.1                        | Use of Macros                                 | 49       |

| 8.1.1                      | Standard Macros                               | '49      |

| 8.1.2                      | User Defined Macros                           | 49       |

| 8.1.3                      | Software and Hardware Replacements            | 50       |

| 8.2                        | Macro Declarations                            | 51       |

| 8.2.1                      | Syntax                                        | 51       |

| 8.2.2                      | Parameters                                    | 52       |

| 8.2.2.1 Macroparameters    |                                               |          |

| 8.2.2.2 Numbering of Names |                                               |          |

| 8.2.2.3                    | Special Labels                                | 54       |

| 8.3                        | Controlled Application of Macros              | 54       |

| 8.3.1                      | RECMAC                                        | 54       |

| 8.3.2                      | Blocks                                        | 55       |

| 8.3.3<br>8.4 <i>A</i>      | Order of Macros<br>application Rules          | 55<br>55 |

|          |                                    | Page |

|----------|------------------------------------|------|

|          |                                    |      |

| 8.4.1    | The Test                           | 55   |

| 8.4.2    | The Application                    | 56   |

| 8.5      | Standard Macros                    | 56   |

| 8.5.1    | GOTO                               | 57   |

| 8.5.2    | FOR Loop                           | 57   |

| 8.5.2.1  | Setup                              | 57   |

| 8.5.2.2  | Condition Test                     | 58   |

| 8.5.2.3  | Updating and Return                | 58   |

| 8.5.3    | WHILE Loop                         | 59   |

| 8.5.4    | Conditions                         | 59   |

| 8.5.4.1  | Conditional Statement Blocks       | 59   |

| 8.5.4.2  | Conditional Operands               | 60   |

| 8.5.4.3  | Conditional Functions              | 61   |

| 8.5.5    | CASE Statements                    | 61   |

| 8.5.6    | Subroutines                        | 62   |

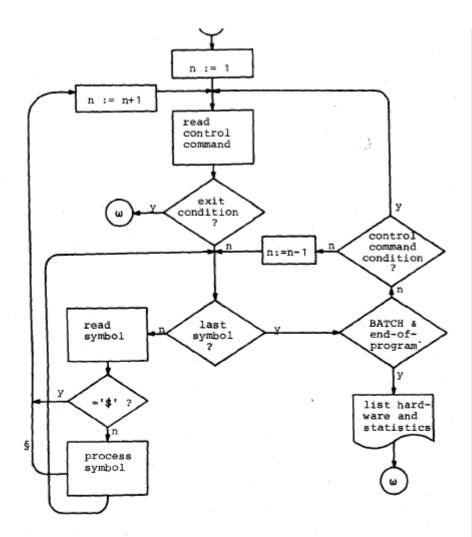

| 9. CONTR | OL LANGUAGE                        | 64   |

| 9.1      | General                            | 64   |

| 9.2      | Command Description                | 68   |

| 9.2.1    | General Commands                   | 68   |

| 9.2.2    | Macro Commands                     | 71   |

| 9.2.3    | Compiler Commands                  | 71   |

| 9.2.4    | Commands Referencing the Data Base | 73   |

| 9.2.5    | Allocator Commands                 | 76   |

| 9.2.6    | Statistical Analyser Commands      | 77   |

| 9.3      | Example                            | 77   |

|          |                                    |      |

|               |                                     |                                        | Page |

|---------------|-------------------------------------|----------------------------------------|------|

| 10.           | EXAMPLE                             | 3                                      | 79   |

| 10.1          | Output Listing Examples 79          |                                        | 79   |

| 10.2          | Computation of a Bessel Function 82 |                                        | 82   |

| REFERENCES 88 |                                     |                                        | 88   |

|               |                                     |                                        |      |

| APPENDICES:   |                                     |                                        |      |

|               | A                                   | Syntax Diagrams of MIMOLA              | 89   |

|               | В                                   | LR(1) Grammar of MIMOLA                | 101  |

|               | С                                   | Additional Rules                       | 105  |

|               | D                                   | Control Language Commands              | 107  |

|               | E                                   | Hardware Data Structure Listing Format | 108  |

|               | F                                   | Symbol Table                           | 109  |

|               |                                     |                                        |      |

#### 1. INTRODUCTION

This Revision 1 replaces the original report (1). The syntax of MIMOLA has been slightly changed and extended. The hardware declaration and assignment parts have been redesigned. A MACRO feature has been added. A description of the hardware database and the control language of the MSS (MIMOLA Software System) has been added (2,3,4).

MIMOLA is a computer hardware description language (CHDL) and a programming language. It has been developed for the following applications:  $\frac{1}{2} \left( \frac{1}{2} \right) \left( \frac{$

- a. Nonprocedural description of hardware (especially computer hardware),  $\qquad \qquad \text{for declarations (e.g. appl. b.-d.), for education and documentation}$

- Functional description of digital systems, procedural, for top-down design, education and documentation

- c. Algorithmic description of digital processors for optimizing top down hardware design

- $\mbox{\bf d. High-level or intermediate microprogramming language for $p$-code} \\ \mbox{\bf generation}$

- e. Modelling of algorithms or machine instructions on a state transition level for measurements and comparisons.

Other applications are possible. It is not the task of this REPORT to show how problems can be solved using MIMOLA. In chapter 2 some examples are explained to show the effectivity of MIMOLA. More details can be found in (5,6) or will be published.

At this point we will summarize some features of MIMOLA to give a frame for the details in the following chapters.

- 1. The hardware is mainly described on the <u>register transfer</u>

<u>level.</u> Lower levels (e.g. the gate level) can be described, but the notation will not be optimal for this purpose. All modules that are of interest. in the construction of computers today and in the near future, have been included in MIMOLA as language primitives.

Language extensions to new modules can be made by macro definitions or syntax extensions. Thus MIMOLA supports mainly modular and structured hardware solutions with a small number of different modules and simple interfaces, but admits also sophisticated special structures for unusual problems.

- 2. The <u>functional description level</u> is strictly the state transition level of a synchronous automaton. This is normally called the microprogramming level. Thus a very close connection between programs and hardware is achieved.

- 3. Parallelism or <a href="concurrency">concurrency</a> can be expressed in the range of one state transition. Besides this constraint the limits of parallel execution are given by the hardware features only. The execution of parallel or spatial sequential operations is asynchronous, as long as no states are changed. Thus concurrent statements need not be order-invariant (as e.g. in ISPS (7)).

This means that all set and store operations are executed synchronously, thus avoiding racing problems. All other operations are thought to be executed by networks with only one permanent state. Asynchronous feedbacks are prevented by the syntax of MIMOLA.

In some cases operations are too complex to be executed by a network with a reasonable amount of hardware. A compromise can be found by admitting the modules to have internal states not visible to the outside. The activity of "impure" modules has to be controlled by additional signals. It is assumed that the control unit generates an execution sequence as in a data flow graph. Thus no synchronization problems will arise.

4. Asynchronous <u>parallelism</u> including more than one state transition have been excluded as a language primitive. Further investigations are necessary to find a general solution for expressions of this kind on the register transfer level.

Asynchronous parallelism on the processor level can be expressed by distinct MIMOLA programs with appropriate synchronization macros. As long as no method exists to distribute algorithms on more than one processor automatically, our design methods are sufficient to design and optimize one processor at a time.

5. For the use of MIMOLA as a high level programming language a macro facility has been included. Thus expressions are allowed that cannot be directly or uniquely be built in hardware.

Standard macros like IF.. THEN ..., CASE, FOR.... CALL are parts of the syntax. The semantics is assumed to he near to the usual one. The

MIMOLA to his ideas or to a special HLL.

Additional user macros can be used to extend the language, to introduce unusual constructions (e.g. synchronization primitives). Thus experiments with different macro-replacements are possible.

6. <u>Data types</u> have been included only as far as they concern the hardware. This is due to our main applications b. and c. Words of different sizes, fields of words and concatenations of words or fields are the only data structures in MIMOLA that can directly be translated into hardware.

Array element references are included as a standard macro. Field declarations can be used for PASCAL RECORD-fields. Distinctions between different scalar data types can be expressed by different memory module names and different operator functions. Different memory names can also be used to express a difference between local and global variables. This represents no limitation for the hardware design space, since modules with different names can be easily merged by an edit process.

7. As CAD systems tend to become too large and inefficient, a LR(1) grammar (Appendix B) has been chosen with additional restrictions to simplify the syntax analysis.

These features could not be found in any other language. This is the only reason for the definition of a new language. It was originally written for our own research. But since our

MSS is written in PASCAL, it can be run on many installations. This may encourage other groups to use MIMOLA together with MSS.

## 2. APPLICATIONS

MIMOLA was designed as a tool. Therefore examples for the applications listed in Chapter 1 are given. They are partly selfexplaining. For details refer to the appropriate chapters in this report.

## 2.1. Nonprocedural Description of Hardware

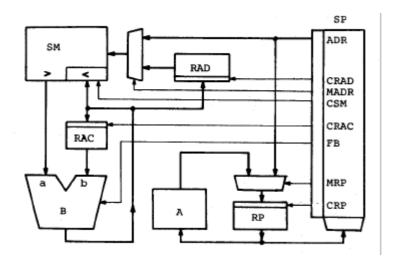

The simple processor in fig. 2.1 can be expressed by the DECLARATION in example 2.1.1  $\,$

Fig. 2.1 Simple Processor

```

DECLARE

ADDMODUL

SM<A(16384:0).BIT(15:0), SM>A

"main memory, 16k, 16 bits, 2 ports",

SP(1024:0).BIT(21:0) "microprogr.mem.",

RAC.BIT(9:0) "accumulator",

RAD.BIT(15:0) "address register",

RAC.BIT(15:0) "accumulator",

A(.INCR) "monadic operator",

B(+,-,.a,.b) "adder",

I.BIT(21)CRP.BIT(20)MRP.BIT(19:18)FB

.BIT(17)CRAC.BIT(16)CSM.BIT(15)MADR

.BIT (14) CRAD.BIT (13:0) ADR

"microprogram word, field names";

ADDCONNECTION

"declaration of data, address and

control paths"

B<a <- SM>A, "memory out to adder input"

B<b <- RAC,

B.FCT <- I.FB "microprogram field to

adder function control",

RAC <- B "adder out to accumulator",

RAC.CON <- I.CRAC "accu load enable",

RAD <- B, RAD.CON <- I.CRAD,

SMcA < - B, SMcA.CON <- I.CSM,

SM.ADR <- I.ADR /RAD "address field

and address register via multiplexer

to address port of memory",

SM.ADR.MPX <- I.MADR "address multi-

plexer control",

RP <- A / I.ADR, RP.CON<- I.CRP, RP.MPX <- I.MPR,

A <- RP, SP.ADR <- RP;

ENDDECLARE

```

Example 2.1.1: Declaration of the Processor in Fig. 2.1

Besides some additional informations, the description in example 2.1.1 has no value of its own, because Fig. 2.1 gives a clearer view of the structure. In the MIMOLA design systems hardware descriptions are used as an input form for computer aided designs and transformations. The DECLARATION can be used to show that the processor in Fig. 2.1 is able to execute a given set of functions. The MSS would give an error output otherwise. It can also be used to translate algorithms to microprograms for this processor.

Another way of hardware description is of more interest: the definition of upper limits in the design space (Example 2.1.2). The meaning is: one memory SM with a maximum of 6 ports is the only memory. No more than three dyadic operators are allowed, B3 with a limited function set. All other recources are not limited. This uncomplete description is the normal way to interact with the MSS process.

#### DECLARATION

ADDMODUL SM(65/535:Ø). WORD.MOREPORT(6), B1,B2,B3 (+,-);

Example 2.1.2

#### 2.2. Functional Description

A computer can well be characterized by a description of its machine instruction set. Only a part of the hardware is visible in this description. The hidden part is of no direct importance to the function the user of the computer sees. This "functional description" can be formalized by a CHDL. Due to our familiarity with programming languages procedural descriptions are more natural to express sequential microprogram steps or state transitions than nonprocedural ones. The description level depends on our purpose.

LSTAA SM(m/RIX -> B(+)) := RACCA, RCOND.N:= RACCA.BIT(7), RCOND.Z:= RACCA -> A(=O), RCOND.V:= O;

> "RACCA accumulator A RIX indexregister RCOND condition register"

Example 2.2.1 : Functional Description of the

M6800 Instruction "STAA m,X"

```

Example 2.2.1 shows a high level description of a MOTOROLA

M6800 microprocessor instruction. It is sufficient for an

ASSEMBLER programmer to understand the function of the

"store accumulator A indexed in memory, address m". In a

design process this description opens the greatest design

```

Example 2.2.2 gives more details about the instruction format and the program counter RPC behaviour.

```

LSTAA1

RIR := SM(RPC),

RPC := RPC -> A(.INCR);

LSTAA2

RHLP:= SM(RPC),

RPC := RPC -> A(.INCR);

RHLP:= RHLP/RIX -> B(+);

LSTAA3

LSTAA4

RCOND.N:= RACCA.BIT(7),

RCOND.Z:= RACCA \rightarrow A(=0),

RCOND.V:= O;

LSTAA5

SM(RHLP):= RACCA;

"RIR instruction register

RHLP internal register"

"RIR

```

## Example 2.2.3 : Possible $\mu$ -instruction sequence of "STAA m.X"

In Example 2.2.3 the instruction is resolved in 5 microstatements. This might be the execution sequence of the M6800 and a description of all instructions of the M6800 in this manner would lead to a structure very close to this microprocessor.

It can be seen from these examples, how useful a functional description of a computer in MIMOLA may be in documentation and education. But every level can also be used as an input to the MSS to find different hardware structures. These will meet the requirements correctly and can be optimized with different constraints and goals.

## 2.3 Algorithmic Description

It has been shown in 2.2 that different description levels are possible with one language. without passing a sharp border we can increase the level of example 2.2.1. User problems seldom bother with details like data storage in registers. Normally transformations are applied on variables or more general data structures. The translation to register load and store operations is a necessity due to the lack of more powerful or simply suitable instructions.

If we want to design optimal structures from the users view, we must start on the users level. Problems can only be solved by computers using algorithms. Therefore a description on the "algorithmic level" is the main application of MIMOLA. Example 2.3.1 shows a short program in three different languages. The postfix-notation of MIMOLA may be unusual, but the correspondences can be found easily. The differences to example 2.2.1 are only gradual. But the point of view differs:

Example 2.2.1 describes the real function of the hardware. The only uncertainty is the probability of occurance. All functions can be listed completely.

```

PASCAL

min := list [1]; max:= min;

for i:= 1 to (n div 2)-1 do (* n odd

begin p:= list [2*i]; q:= list [2*i+1];

(* n odd *)

if p>q then

begin if p > max then max:= p;

if q < min then min:= q

end

else

begin if q > max then max:= q;

if p < min then min:= p

end

end;

FORTRAN

min = list (1)

max = min

DO 20 i = 2,N-1,2

p = list (i)

q = list (i+1)

q = list (1+1)

IF (p.LE.q) GOTO 10

IF (p.GT.max) max = p

IF (q.LT.min) min = q

GOTO 20

IF (q.GT.max) max = q

IF (p.LT.min) min = p

10

20

CONTINUE

MIMOLA

S(min) := S(list[1]),

S(max) := S(list[1]),

FOR i FROM 2 BY 2 TO S(n) \rightarrow A(.DECR);

L1

L2

DO(i)

IF S(list [D(i)]) = V1/

S(list [D(i) > A(.INCR)]) = V2

->B(>)

THEN IF V1/S(max) ->B(>)

THEN S(max):= V1 FI,

IF V2/S(min) ->B(<)

THEN S(min):= V2 FI

ELSE

IF V2/S(max)->B(>)

THEN S(max):= V2 FI,

IF V1/S(min)->B(<)

THEN S(min): = V1 FI

FI,

OD(1);

```

## Example 2.3.1

Example 2.3.1 shows a possible function. We can estimate the probability but we cannot give a limited list of all algorithms. This is an additional degree of uncertainty. It can partly be overcome by using large samples to be able to calculate "precise" mean values. Due to the lack of knowledge about user behaviour and therefore the difficulty of giving an exact task description of the design object, "precise" is very relative.

Large program samples ask for a descriptive language with high-level language features. This is an unusual demand for CHDL's but had to be met by MIMOLA.

A set of algorithmic descriptions define an automaton or hardware structure. The microinstructions of these programs cause state transitions of this automaton. Different automatons can be found by transforming these programs. On the other hand, manual changes of this automaton (by declarations, see 2.1) can cause transformations of the programs to preserve the ability of execution.

Thus the hardware can be tailored to meet constraints and a proof is given at the same time about the correct execution of the programs on this hardware. Since the programs form the task description, the correctness of the solution can be proven.

To find an optimum, the variations of the hardware are not done arbitrarily. As the design space is too large to-try all possibilities, occurence probabilities are calculated for all

resources (e.g. modules, connections, instruction word fields) to guide the variations.

This is a very short description of our design method. It is implemented to a large extend in the MSS (MIMOLA Software System). The use of functional descriptions (Chapter 2.2) is a special case of the method. A better description is (6).

## 2.4 Microprogramming Language

A welcome byproduct is the possibility to use MIMOLA as a high-level microprogramming language. This is due to the fact that the state transition level is a basic language feature and is preserved during all transformations. For all MIMOLA programs an automaton or hardware structure exists that can execute the microstatements of the programs without further transformation. As already mentioned in 2.3 a change of the automaton causes a program transformation. A complete declaration of a computer structure (see chapter 2.1) can be seen as a change of this kind. Thus the MSS will respond with transformed programs executable on this structure. Since these programs describe state transitions, they contain the microcode in a special form. Some decoding and software tasks like storage management have to be added to change the MSS to a microprogram compiler. This application is under investigation.

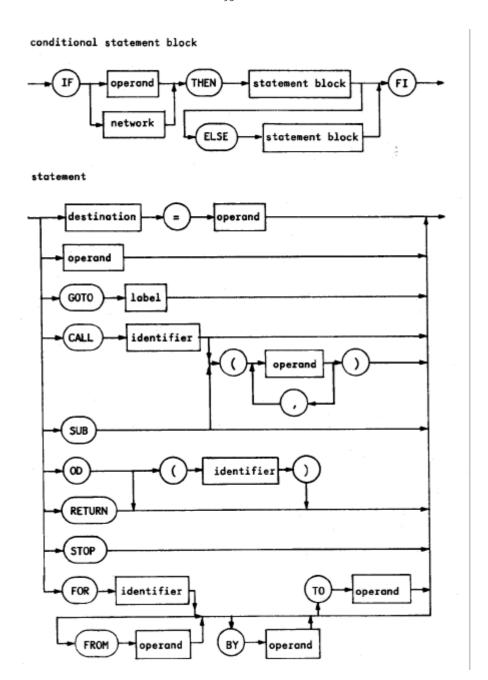

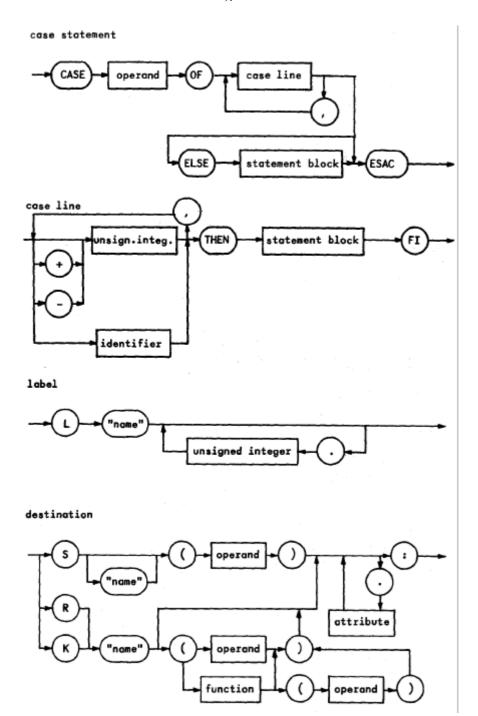

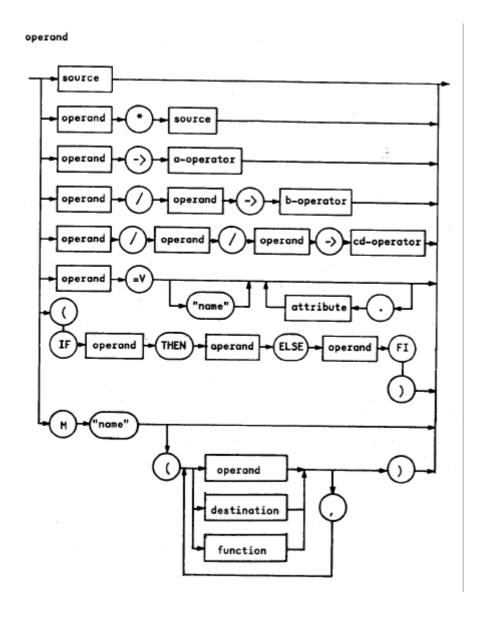

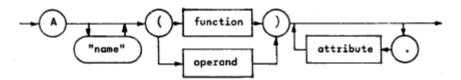

#### 3. SYNTAX

The syntax of MIMOLA is defined in two ways. The user can refer to the syntax diagrams in Appendix A. The syntax analyzer of the MSS (MIMOLA Software System) takes a production system in Backus notation, listed in Appendix B. It is  ${\bf an}$  LR(1)grammar.

Additional rules are listed in Appendix C. They are used by a preprocessor in front of the syntax analyzer.

Part 1 is necessary to guarantee correct hardware functions.

Part 2 is additionally required to suppress meaningless programs.

$\ensuremath{\mathtt{A}}$  violation of theses rules does not necessarily lead to hardware errors.

The symbol set of MIMOLA is 96 characters of ASCII.

Provisions are made to allow for 64 character sets. Throughout this report the following meta symbols are used:

- ::= equivalence in Backus notation

- < > include nonterminal symbols

- " " include representatives of strings of terminal symbols

- $\left\{\begin{array}{ll} \prod_{n=1}^{m} & \text{contents may be repeated at least n times and} \\ & \text{at most m times (BNF)} \end{array}\right.$

- \* A star \* is used if the contents may be repeated indefinitely.

symb-1|symb-2 means: symb-1 or symb-2

For different purposes four special adapted sublanguages exist:

assignment language, declaration language, macro language, program language. The grammars of these languages differ only slightly. The differences are marked in the syntax diagrams and the list of rules and will be explained in the following chapters.

A MIMOLA string may contain a sequence of different language parts. Fig.  $\,$  3.1 shows the endsymbols.

| State       | Control key   | Endsymbol |

|-------------|---------------|-----------|

| Assignment  | ASSIGN        | ENDASSIGN |

| Declaration | ADDMODUL /    | ,         |

|             | ADDCONNECTION |           |

| Macro       | MACRO         | ENDMACRO  |

| Program     | PROGRAM       | END /     |

|             |               | ENDSUB    |

## Fig. 3.1

Different language parts may be <u>nested</u> either by writing a \$-sign into the current source string or by using preprogrammed breakpoints (see chapter 9.1). Both conditions cause MSS to expect a (nested) new command key. Example 3.1 gives valid combinations of control commands.

ADDMODUL R1,R2; "level 1: addition of modules"

PROGRAM "level 1: start of program"

begin LØ R1:= R2;

\$ASSIGN a:= Ø; ENDASSIGN "level 2: nested assignment"

L1 S(a) = R1 ; "continue with level 1"

end "end-of-program causes the

command to be read from

terminal for non-BATCH jobs"

PRINTHARDWARE

EXIT "exit from MSS"

#### Example 3.1

The set of allowed control commands depends on the context. It is not allowed to put two or more identical control commands in one nesting hierarchy (e.g. a PROGRAM part may not contain a PROGRAM command).

Assignment parts provide means to define software equivalences with no direct influence on the hardware. They are tools for program structuring and microcode generation, syntax analysis starts after "ASSIGN". A correct assignment part can be reduced to the assign-axiom, when the endsymbol "ENDASSIGN" has been found. If equivalences are not changed by other assignments, they are valid until exit from MSS.

<u>Declaration-parts</u> are used for unprocedural definitions or changes of hardware structures. For correct parts a syntactical reduction to the declaration-axiom is possible, when the endsymbol "; " has been found. Hardware structures are valid until exit from MSS if they are not changed by

ADDMODUL and ADDCONNECTION commands or deleted with DELMODUL and DELCONNECTION commands.

Macro parts allow the declaration of macro equivalences and replacements (see chapter 8). Definitions start with \$MACRO and stop with ENDMACRO. Macro ranges are blockoriented in order to allow easy conversion of variable declarations of high-level programming languages. A block is opened by a \$\begin{center} 1 \\ 5\end{center}\_0 BLOCK command and closed by \$\begin{center} 5 \\ 1\end{center}\_0 ENDBLOCK. The first block is preopened.

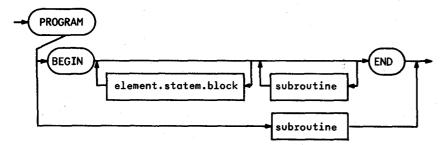

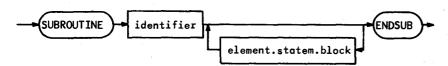

The <u>program parts</u> contain the algorithmic or functional descriptions. Program parts generate hardware descriptions and statistical analyses if applied to the MSS. Program parts may be subdivided in main program parts, enclosed in BEGIN ... END, and subroutines enclosed in SUBROUTINE ... ENDSUB. The syntax analysis is separately applied if these parts are disjunctive. Nested subroutines are analysed together with the enclosing program.

## 4. HARDWARE DATA STRUCTURE

The MSS stores all information about the available hardware together with the statistical information in a hardware data structure (hds). The structure is similar to the network model of data bases.

Most of the entities are hierarchically ordered:

4.1. Group, Module All modules with the same initial letter form a group.

The MSS recognizes the following groups:

- monadic operator, dyadic operator, Α

- B

- С

- triadic operator,

Do Loop variable storage,

hardwired constant, D

- microinstruction, I

- K

- stack, network, N

- R

- register, storage (RAM), S

- non-stored result.

## 4.2 Port Input

\_\_\_\_A module has at least one <u>port.</u> All input and output is

via ports. There are input ports, output ports and

bidirectional

ports: Portdirections may be specified by ' < ', ' > ' or '<

a fixed number of ports (e.g. dyadic operators have three: two for input and one for output); others have a varying number of ports (e.g. random access memories). There are certain limitations to the set of allowed portnames and directions, depending on the group which the module belongs to:

The control language command NOLOWERLETTER changes the above lower case letters to upper case letters.

Each port has up to four <u>inputs</u> or <u>outputs</u>: a <u>function input</u>, an <u>address input</u>, a <u>control input</u> and a <u>data input</u> or <u>output</u>. They are selected by the reserved attributes .FCT, .ADR, .CON and .DAT. The latter is assumed by default.

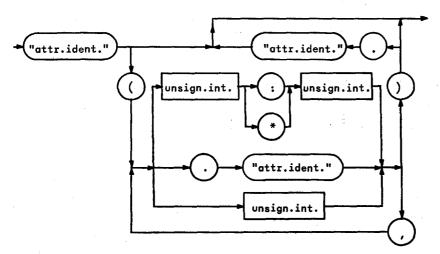

#### 4.3. Field

Inputs and outputs have <u>fields</u>. These may be ranges of bitnumbers or attributes which stand for unassigned ranges of bits (called <u>bitattributes</u>). Any attribute which is not a predefined attribute, is considered to be a bitattribute. The bitrange of a bitattribute can be defined in the ADDMODUL declaration.

Input fields can be viewed as multiplexers if there is more than one connection for a field. In this case the field has an associated multiplexer address input field which the user can select with the .MPX attribute.

#### 4.4. Connection

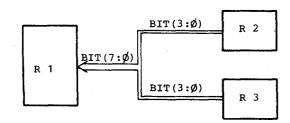

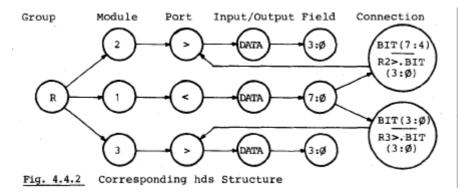

Connections in their most general form are concatenated subranges of data fields of outputs. Connections are the hds representation of bundles of wires connected to a destination. For example the block diagram of Fig. 4.4.1 is transformed into the nodes of Fig. 4.4.2.

$\underline{\text{Fig. 4.4.1}}$  Hardware Block Diagram

The hds description of connections contains independent ranges for source- and destination bits. See chapters 5.3. and 5.4. for additional information.

## 4.5. Data Structure Entries

The following is a list of some of the entries in the just described hierarchical part of the hds:

boolean value indicates whether or not a group :

module of this group has been declared in the

declaration or not.

module :

number of possible duplicates, pointer to joint distribution table, number of additional ports allowed,

frequency of use,

distribution of concurrent uses of ports of this

module.

port :

frequency of use, pointer to entry in joint distribution table

(S and K only), list of functions, default function, boolean value indicating the right to add more functions to the list of functions.

field :

frequency of use, pointer to entry in joint distribution table

(uinstruction only)

symbolic value (microinstruction only) frequency of use, multiplexer address,

connection:

inhibit flag from \$DELCONNECTION command.

Other tables in the MSS are:

1. Second order joint distributions for the

use of modules and storage ports.

2. Second order joint distributions for the use of the microinstruction fields.

- All the above tables are.listed by \$PRINTHARDWARE and \$TYPEHARDWARE.

3. Frequency of function uses, listed by \$PRINTFUNCTIONS and  $\mbox{\ensuremath{\mbox{\$TYPEFUNCTIONS}}}$  .

4. Overlapping status for bitattributes. 5. Label

table.

6. Identifier table (not yet implemented).

#### 5. DECLARATION

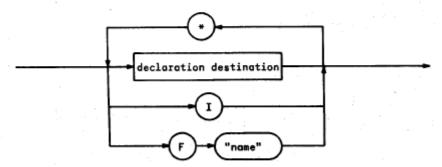

5.1. Declaration of Modules, Ports and

## 5.1.1. Addition

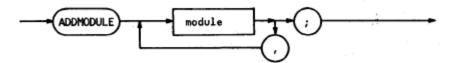

Hardware modules, their ports and multiplexers can be declared with the \$ ADDMODUL command. The command key must be followed by a list of hardware descriptors.

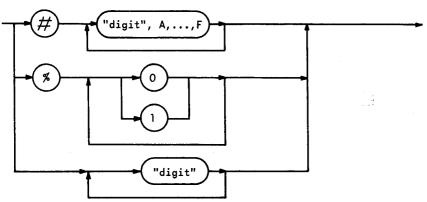

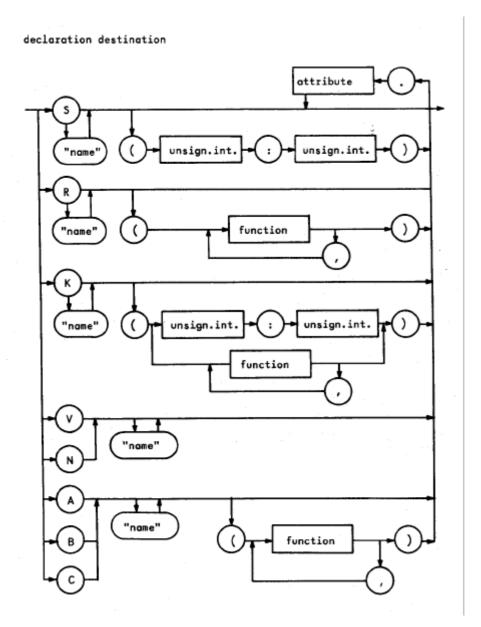

The general form of the syntax is:

<descriptor>::= <modulename> { <direction> <direction>

${\text{-}}_{\text{o}}^{\text{-}}$  {.  $\text{-}}_{\text{o}}^{\text{-}}$

<functionlist> ::= ( <function>  $\{, <function>\}_0^*$  )

<addressrange> ::= ( <unsigned integer> : <unsigned integer> )

Complete syntax rules are given in Appendix B.

## ADDMODUL

$S <> (\# FFFF:\emptyset).BIT (31:\emptyset)WORD,$

"RAM of 64K cells of 32 bits which are named WORD" BALU (+,-,.AND,.OR,.XOR).BIT(32)CARRY.WORD,

"arithm.-log. unit with functions and a CARRY output" BALU < a. WORD. INPUTMAX (2). NOMOREFIELDS;

"the a input of BALU is 32 bits wide, has a maximum of two inputs to the multiplexer, no other fields are allowed"

Example 5.1.1

All ports, inputs, and outputs may be specified separately.

If no direction is present, output is assumed. Default portname is 'A' for RAMs and stacks and (blanks) otherwise. .DAT is default for inputs and outputs.

Continuous bit ranges used in ADDMODUL will not be concatenated. R1.Bit (7:3,2:0) will generate two fields if used in ADDMODUL, but only one field BIT $(7:\emptyset)$  if it is a creating call in a PROGRAM part. A list of reserved attribute names is used for entering more information into the hardware data structure:

#### a) DUPLICATE ( ui) /NODUPLICATE

DUPLICATE means: this module may be duplicated ui times if necessary. If ui is omitted, a default value of 26 is assumed. Maximum value of ui is 26. NODUPLICATE is equivalent to DUPLICATE (O). If no DUPLICATE attribute is present, a value of 26 is assumed for A and B-operators declared outside of ADDMODUL and Ø otherwise. Duplicates may not be duplicated again.

If the number of temp-registers RHLP needed for the sequentialization of a program is insufficient, the compiler creates a new one if the duplicate entry of RHLP is greater than zero. The new register will be named RHLP\_xxx, where xxx is a number of three digits.

If an A or B-operator is used more than once in an esb, the compiler tries to duplicate the existing A- or B-operator.

The new name will be oldname\_character. 'Character' will be incremented from A to Z. The underscore character '\_' will overlay the first blank character of the old name or the 7th character if 'oldname' has 7 or more characters.

Duplicates have the same functions and field. extend parameters of the output port and the same trace option as the original module. Fields are not copied.

b) MOREPORTS (ui ) /NOMOREPORTS MOREPORT means: this module can have ui more ports than declared. If ui is omitted, a default value of 26 is assumed. Maximum value of ui is 26. NOMOREPORTS is equivalent to MOREPORTS (0). If no MOREPORT attribute is present, a default value of 0 is used for modules declared in an ADDMODUL declaration and 26 otherwise. ui is decremented for each created port. If the present number of ports of a storage S or stack K is insufficient, the compiler generates a new one if the moreport entry is greater than zero. The first character of the alphabetically last portname will be incremented by one in order to generate a new name. c) MOREFCT /

If functions for a port have been declared in ADDMODUL, the list is assumed to be complete. Addition of more functions by appearance in the program part is possible, if the user uses the MOREFCT option. If functions have not been declared, the addition of functions is allowed. If the user wants to stop the addition of functions for such ports, he may use the NOMOREFCT attribute. The list of functions influences the final statistics in two aspects: 1. The computation of microinstruction bits

$n_F = \sum [ld(number of functions of this port)]$ all ports

2. Predeclared duplicates of operators may have different function sets. The allocator uses a specific 'duplicate' only if the specified function is allowed for that port; that means either the function must be present or the addition is allowed.

#### d) AUTO/NOAUTO

The automatic execution of functions may be switched on and off with AUTO and NOAUTO. .LOAD for register and storage destinations and .PUSH for stack destinations are executed by default. This option only influences counts of functions.

e) AUTOFCT (function )

This attribute defines the function which should be executed by default when that particular port is referenced. Unimplemented at this time.

#### f) INPUTMAX (ui)

This attribute limits the number of inputs to a multiplexer (field). Preceding attributes .DAT, .ADR, .FCT, .CON, .MPX and bitattributes may be used to select the field. If there are preceding bitnumbers/names, the limitation will apply to these bits, otherwise they will be default limits for all newly created fields. If no INPUTMAX is present, a number of 4096 will be used.

ADDMODUL

B.FCT.BIT(3:0). NOMOREFIELDS.INPUTMAX(1);

Example 5.1.2

## g) TIME (ui)

This attribute defines maximum delay times for fields. If no field is specified, it is valid for all fields of an input or output; otherwise it is valid for one field. Default value is 1.

Field dependent run-time estimation is not yet implemented.

## 5.1.2 Deletion

Modules may be deleted by \$\begin{cases} 1 \\ 0 \end{cases} DELMODUL < module name > . Connections from ports of this module are not automatically deleted. Instead, their source module name will print as !DELETED.

#### 5.2 Standard Modules

## 5.2.1 Random Access Memory

S "name" ( <operand> )

In software this means the value of a variable or the contents of a memory cell with the effective address <operand> . The word length is determined by the data type. This cell can be read as a source or altered as a destination.

In  $\underline{\text{hardware}}$  S represents a data output or input port of a word-oriented RAM. The operand is connected to the address lines of the RAM.

Parts of memory words can be addressed by attributes:

S "name" ( <operand> ) <attribute>

The allocator tries to find a suitable port if "name" does not contain a portname.

#### 5.2.2 Register

#### R "name"

defines a register. Every register is a module of its own with  ${\bf data}$  input and output. In contradiction to memories S, it to stores only one word. The modules must be identified by names.  $\sim\!i$ . Names can be declared in the declaration part.

Registers are unnecessary from the viewpoint of algorithms. Therefore they should be avoided on level 0 of MIMOLA. Exceptions are registers with special functions, e.g. the program counter RP, I/O-registers.

Some registers can perform functions:

R "name" ( <function> ) The functions are executed synchronously to the <esb> clock (see chapter 7.1.3). Only the function  $\underline{.LOAD}$  is a standard function, if R is a destination.

Functions can be coded by the value of an operand:

#### R "name" ( <operand> )

The code must be declared.

Functions can be made depending on operands:

```

R "name" ( <function> ( <operand> ) )

```

By this e.g. the number of shifts can be made variable.

## 5.2.3 Stack

## K "name"

defines a stack. An algorithm can use more than one stack. Therefore every stack must be named. This can be done as in the case of registers. The standard depth of a stack is infinite. A finite depth can be declares. The expression  $\underline{K}$  "name" addresses

K "name" ( <operand> ) all data in the stack can be addressed.<Operand>= 0 addresses the top of the stack while reading or writing. Positive values point down the stack. Writing into the stack should be avoided. Using an <operand> , no stack function is executed.

The only standard function <a href="PUSH">.PUSH</a> is executed automatically, if K is a destination. All other functions can be declared in a declaration part or be appearance in the program, as long as no other declaration has appeared. Possible functions are:

.PUSH, .POP, .NOPUSH, .NOPOP, .CLEAR, .POINT

Only the function .POINT must be explained. Sometimes the stack

pointer must be examined to estimate the load of the stack.

K "name" ( .POINT ) addresses the stackpointer. By this the value of the address of the top of the stack can be read or changed. The bottom of the stack has the address (b.

## 5.2.4 Instruction

I is the current instruction word and is an abbreviation of  $\underline{S}$   $\underline{(RP)}.$  There is resemblance to the "instruction register" in conventional structures, but I is no register and therefore no "instruction fetch phase" is needed. Such a phase can be programmed, if conventional cumputer structures shall be exactly simulated. By

#### I. <attribute>

every part of I can be addressed. These parts may be functions, addresses, constants etc. Thus the microprogram can be inserted

As long as the precise partitioning of the microprogram word is not fixed, the implementation by the instruction word can be expressed by:  $\mbox{I ( <i dentifier> ) } \qquad \mbox{and}$

I ( <function identifier> )

## 5.2.5 Hardwired Constant

F "name"

is a single hardwired constant. The storage of several constants in a  $\ensuremath{\mathsf{ROM}}$  can be expressed by

F "name" (<operand>) The operand addresses the ROM. Single constants and the contents of the ROM must be declared. Hardwired constants are one possibility to implement constants (see chapter 7.5.2).

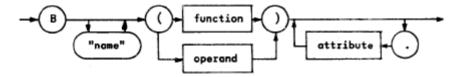

## 5.2.6 Monadic Operator

## A "name" ( <function> )

denotes an operator with one data input and one data output. It performs a monadic operation on one operand standing left of it.

Standard operations for all applicable data types are, output type equal to input type:

- .NOT .ABS .INCR .DECR

boolean output:

.SIGN

$$<\emptyset$$

$<=\emptyset$   $<>\emptyset$   $>=\emptyset$   $>\emptyset$

By

## A "name" ( <operand> )

the function code can be replaced by an operand, if this code has been defined. This is a possibility to control operations by-passing the control module. If it is used at all, great care must be applied. Attributes can be applied.

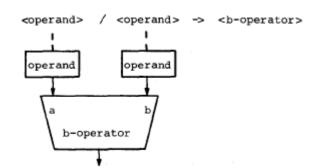

## 5.2.7 Dyadic Operator

## B "name" ( <function> )

denotes an operator with two data inputs a and b and one output. It performs dyadic operations on the two operands standing left of it. a and b are standard names and can be used to express functions. The assignment to the ports of the operator is explained in chapter 5.4.1.

Standard operations for all applicable data types are, output type equal to input types:

+ – \* / –a+b .AND .OR .XOR .NAND .NOR Boolean output:

Other features are the same as in chapter 5.2.6.

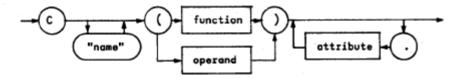

# 5.2.8 Triadic Operator

## C "name" ( <function> )

C has 3 input ports named a, b and c. The assignment to the operands is an extrapolation from that in chapter 5.2.7.

No standard functions are declared. Other features are the same as those in chapter 5.2.6.

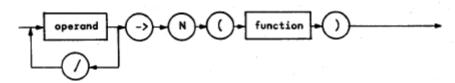

#### 5.2.9 Network

## N "name" ( <function> )

denotes a network with any number of inputs, named a, b,  $\dots$  A, B  $\dots$  from the left to right. Operands are assigned in the same order.

Functions are expressions of used input names and operators  $% \left( 1\right) =\left( 1\right) \left( 1\right)$

(AND )

(OR )

- (NOT ).

No brackets are allowed.

It is assumed that every control unit of a computer has an instruction pointer unit (8). This unit performs the switching in the case of conditional instructions and is therefore equivalent to the operator td. The range of functions can be altered by declarations.

#### 5.3 Declaration of Connections

#### 5.3.1 Addition

Connections are added by the \$ ADDCONNECTION command, followed by a list of connections The general form is

$\{\$\}_0^1$  ADDCONNECTION <connection> $\{$ , <connection> $\}_0^*$ ;

#### ADDCONNECTION

## Example 5.3.1

#### 5.3.2 Deletion

Deletion of connections is started by the  $\{\$\}_0^1$  DELCONNECTION command. General syntax is the same as in 5.3.1. Deleted connections remain in the hardware data structure; they are marked as non-usable and are not counted as multiplexer inputs.

# $\underline{\text{Example 5.3.2}}$ : DELCONNECTION Va <- Rb ,

# 5.4 Data Paths Conventions

The standard declaration for data paths is: All inputs and outputs of all modules are connected via multiplexer. The number of paths can be limited by declarations (chapter 5.1.1) .

# 5.4.1 Statements

In the case of

#### <destination>::= <operand>

specifies a connection between the data output of <operand> and the data input of <destination> , which must be a memory. The <operand> itself can include the connection of several

Fig. 5.1

The assignment of the input and output ports is always given by the position of the operands. The postfix-notation gives a simple unique picture of all data paths. The switches for different data paths are assumed to be multiplexers, assigned to the inputs of the modules. It is possible to declare busstructures.

#### 5.4.2 Destinations

All destinations are assumed to be edge triggered. This means: the contents of a memory cell can be read and changed in the same <esb>

#### 5.4.3 Bit-to-Bit Assignment

the word length has not yet been specified.

Normally, when equal data types are coupled, bits with equal bit-position are connected. The rightmost bit is always the least significant bit. Its bit-position number is zero.

If data types with unequal word length are coupled, the connection is always right justified. There is no truncation, if

Free input lines are set to zero, free output lines remain open ended. Information can be lost. Correct type transformations must be made by operators.

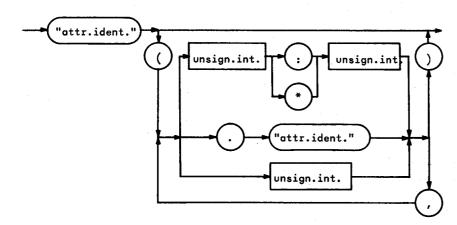

#### 5.4.4 Attributes

All data paths can be split up into single bits, bitgroups or

is a direct assignment. The expression may be composed of several parts, separated by commas. See also Appendix A. The meaning of these parts is:

<unsigned integer>

<unsigned integer>

is a range of bits/bytes.

<unsigned integer > is the bit/byte-position

number of a single bit/byte. Allowed names are:

BIT, BYTE;, MASK; BYTEMASK+

BIT and MASK address bits.

BYTE and BYTEffASK address bytes.

BIT and BYTE effect the position of the bits/bytes. All selected bits/bytes are packed tight to the right bound of the data path.

MASK and BYTEMASK do not effect the position of the bits/bytes. The rules of chapter 5.4.3. have to be obeyed.

Two examples show the result of attributes to bit connections:

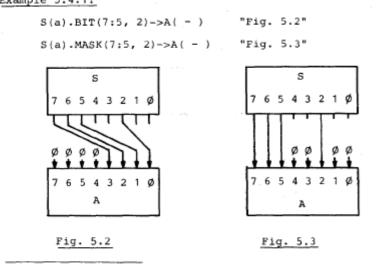

# Example 5.4.1:

<sup>&</sup>lt;sup>+)</sup>not yet implemented

#### 5.4.5 Distributors

V "name" marks a point on a data path. By

${\tt V}$  is used in the  ${\tt declaration}$  part it denotes a bus-structure

(see chapter 5.3.1).

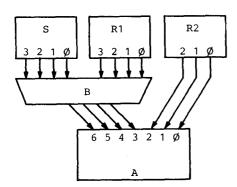

#### 5.4.6 Concatenation

#### <operand> \* <source>

means the concatenation of all bits of the data output of <operand> with those of <source> . The result forms a new data path, whose width is that of the sum of both elements. The source forms the lower significant part of the word. Example 5.4.2 shows this relation.

# Example 5.4.2:

S(a) /R1 -> B(+) \* R2 -> A(-) "Fig. 5.4"

Fig. 5.4

With  $\boldsymbol{V}$  as <source> , even complicated connections can be made.

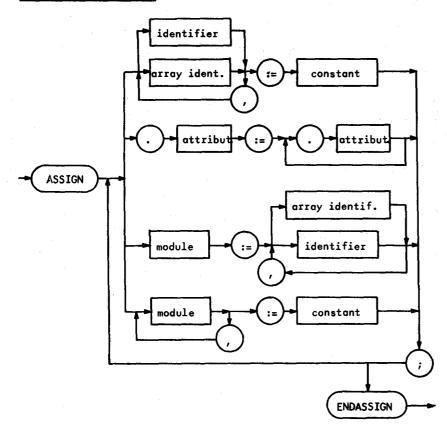

#### 6. ASSIGNMENTS

The assignment part has little or no relevance to the design of the hardware. It is needed only when micro programs shall be generated. The assignment part is bounded by ASSIGNMENT ....

ENDASSIGN The assignment statement a:= b; means: b is assigned to a. a and b may be lists. There are four kinds of assignments:

# 6.1. Identifier Assignment

#### 6.2. Storage Map Assignment

#### 6.3 Initial Value Assignment

# 6.4 Record Assignment

# 6.5 Example

# ASSIGNMENT

```

a,b,c,d: = Ø; "identifier assignment"

j,k,l := 1;

S(1ØØ:Ø):= top, last, ar [5Ø:Ø]; "storage map"

"equiv. to: ar:= Ø; last:=51; top:= 52;"

R1,S(5Ø:Ø):= Ø; "initial value"

.A:= .B.C.D ; "record assignment"

.B:= .E.F. ;

.INT :=.SIGN.VALUE;

ENDASSIGN

```

#### 7. PROGRAM

#### 7.1 Fundamental Semantics

MIMOLA is to be understood as a programming language and as a language to describe hardware or synchronous automata functions on a gate control level. Therefore we must notice the software and the hardware meaning of language details.

The fundamental nonterminal symbol of the syntax is the <a href="Months of the syntax"><e syntax</a> is the <a href="Month

The hardware meaning is: one <esb> describes completely one state transition of all synchronous automata that are large and powerful enough to accept all <esb> 's of the programs. To reduce the length of the programs there exist some fundamental semantics:

7.1.1 All storage cells that contribute to the  $\underline{\text{state of the automaton}}$  are not changed except for those explicitly mentioned in the  $\langle \text{esb} \rangle$  and except for the program counter RP.

7.1.2 Unless otherwise determined the program is assumed to be stored in a memory (see 5.2.4) with the <u>program counter RP</u> as a pointer. RP is assumed to be set to the label of the next <esb> in the program, when no other assignments are made.

RP is affected by: GOTO. CALL. RETURN. DO. OD.

7.1.3 All <u>statements</u> of one <esb> are executed within one clock period. Reading of, switching of and operations on data are assumed to be network functions needing no clock. The <u>clock</u> changes the information of the destinations, executes the functions of registers and stacks and terminates the action of the statements by setting RP. The clock is one edge of a clock puls and is <u>synchronous</u> for all statements of one <esb> The clock is not periodic. Its interval depends on the slowest statement in every <esb>

7.1.4 All resources and data paths that occur in one <esb> must be available in parallel. The syntax makes no limitations as to the <u>number of resources or paths.</u> The number can be limited by declarations as a part of the definition of a special automaton. The set of possible resources is defined by the standard declarations in chapter 5.2.

7.1.5 Unless otherwise determined it is assumed that there exists a <u>control module</u>. It must generate the clock, decode the current program word to control the resources and data paths and it must take into account the conditions. There exist no sequential steps within any <esb> controlled by hard-wired or firmware microprograms. The level of MIMOLA is therefore the microprogramming level.

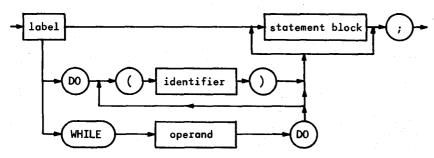

## 7.2 Labels

L "name" (. <unsigned integer>)

Every <esb> begins with a label. It can be used as a line number, as an <esb> address or as a program counter value. The direct assignment between labels and memory addresses of microinstructions is made by the MSS on the lowest level of MIMOLA or by the program loader.

Seven characters are significant for the label name.

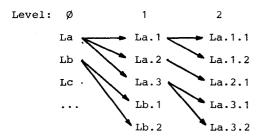

During the design process the MIMOLA programs are often compiled from one level n to the next lower level n+1. Every compilation divides several < esb>'s into smaller ones. The label number space is extended by joining unsigned integers at every change of the level. Thus the level can be evaluated from the label structure.

# Example 7.2.1 :

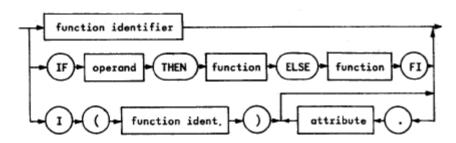

#### 7.3 Functions

The standard functions have been described in chapter 5.2. Special functions have to be declared. It is assumed that the compiler knows the code to control the modules.

Normally the function code is part of the instruction word  ${\tt I.}$  This can be expressed by

$\it IF$  <onerand> THEN <function> ELSE <function>  $\it FI$

#### Example 7.3.1:

```

S(a) = V \rightarrow A(IF V \rightarrow A(<0) THEN - ELSE + FI),

K1(.POP(3)),

```

#### 7.4 Identifiers

Identifiers are representatives of constants. After compiling there should exist a list of the values of all identifiers. There are two kinds of assignments:

- 7.4.1 Identifiers can be assigned a value in the assignment part. These identifiers can be operands. Their values are known to the programmer.

- 7.4.2 Identifiers can be assigned a value by their appearance in a program. Identifiers forming the addresses of memory cells are typical examples. In this case the value of the identifier is the <u>address</u>, not the contents of the memory cell.

The only standard data structure is the array. Elements of arrays can be addressed by  $% \left\{ 1,2,\ldots ,2,3,\ldots \right\}$

exists no fixed scheme for the evaluation of effective addresses of array elements. If array indices shall be compiled, array dimensions must be fixed in the assignment part and an evaluation algorithm must be declared in the macro definition part.

#### 7.5 Operands

#### 7.5.1 General Features

Every point on a data path having unique sources can be an operand.

A switching between operands depending on a condition can be expressed by

( IF <operand> THEN <operand> ELSE <operand> FI )

This construct is equivalent to a multiplexer in hardware.

The root of an operand is the source. Most of the possible sources have been treated in chapters 5.2 and 7.4 .

# 7.5.2 Constants

Standard constants are all sorts of decimal, hexadecimal and binary numbers. Their use in a program implies no hardware solution for their real source:

hardwired: F chapter 5.2

part of instruction word I chapter 5.2

stored in memory S chapter 5.2

Part of the instruction word is default, another choice must be declared by macros. If this choice is clear from the beginning, no constant should be used.

# 7.5.3 FOR Loop Control Variable

Independent of a hardware or software solution of the FOR loop, the control variable value can be accessed by  $\underline{\mathtt{D}}$ . In the case of nested loops, the control variable of outer loops is addressed by

D ( <unsigned integer> )

The number controls the distance to the outer loop. The identity  $D(\phi) = D$  specifies the begin of counting.

Another possibility to access the control variable is

D ( <identifier> )

The identifier must be the control variable of the current or of an outer loop.

#### 7.5.4 Dummy Source

X is a dummy source. It is needed, if an operand has no influence but must be present to fit the syntax.

#### Example 7.5.1

$S(a) \ / \ X \ -> \ B(-a)$  "dyadic operator executing a monadic operation"

IF a THEN X ELSE ... FI "dummy statement"

a / b -> BV(X).EQUAL "operator without function input"

#### 7.6 Allocator Conventions

7.6.1 Default Replacement of Identifiers, Functions and Constants

Any constant, identifier or function, which is not removed by a macro, is substituted by a reference to a field of the microinstruction I. The symbolic name of this field depends on the destination. The first letter reflects the type of the input: A for address inputs, C for control inputs, D for data inputs and F for

on the left. If the field addressed by this string is already set to another symbolic value, a '@' is added on the right, and the following character will be incremented from 'A' to 'z' until a free field has been found. The resulting string is truncated to an implementation-dependent number of significant characters (e.g. 8,12 or 16). Therefore long names should be avoided, especially for modules which may be duplicated.

For example, the operand SM > B ( $\emptyset$ ) will create a connection SM>B. ADR <- I.ASMB and assign  $\emptyset$  to ASMB.

If the NOMOREFIELDS attribute has been written for I and the resulting fieldname is not already a fieldname of I, the allocator will inhibit the new field if the MSS runs in the batch mode. If the MSS runs in terminal mode, it will ask the operator if he allows the new field. The user may allow the field by typing 'Y', inhibit the field by typing 'N', or he may rename it by typing a name not starting with 'N' or 'Y'. Asking will stop for a particular destination after the user typed 'N' for that field. At least one field for a destination is always allowed.

The symbolic values of the fields created in this way may be put out in each <esb> if the  $\left\{ \$ \right\}_0^1$  CODE command is used. In this case the COD-file contains a symbolic microprogram.

7.6.2 Duplicates of Operators

Refer to 5.1.1 a) and 5.1.1 c)

#### 7.6.3 Port Allocation

The omission of port names for stacks and storages indicates that the allocator shall select suitable ports. The allocator then will first try to find a port where the address connection already exists and is usable. If no such port exists, the user may select between taking the first free port by giving the \$FIRSTPORT command and optimizing data connections (default). In the second case the allocator tries to find a port where the required data connection already exists and can be used. If there is more than one port with the required data connection, the one with the most frequently used connection is taken. In case of equal frequencies, the alphabetically first port is taken. This optimization is essential for the design process because it tries to create few frequently used connections instead of scattering uses over the set of all possible connections. The designer's part of the optimization process is to delete some unfrequently used connections (whose usefulness could not be foreseen by scanning only once over the entire program) with the \$DELCONNECTION command. A second pass over the program, started by \$ RESET, will avoid these connections, when this feature has been implemented.

The allocator will create new ports if the current number is not sufficient and if creation is allowed. Creation is allowed either if the MOREPORT entry is greater than zero or if no stack or storage has been declared. If no new port is allowed and the current number is not sufficient, the compiler will split the <esb> .

#### 7.6.4 Default Bitnumbers

If no bitnumbers/names are present in a description of a connection, the allocator inserts default ones according to the following rules:

- 1. If I is the source, chapter 7.6.1 applied.

- 2. If there is no field at the source or destination, the

- attribute .WORD is used.

3. If there is a field present, the field's bitnumbers will be converted into attributes.

- 4. If there are several fields present, bitnumbers/names, which are not overlapping (see chapter 6.4 ) are concatenated in the following sequence: .WORD fixea bitnumbers .INT .REAL .BOOL user-defined bitnames in the order of their appearance in the program <a href="Example 7.6.1">Example 7.6.1</a>

#### Assume:

S<A.DAT contains no field, S<A.ADR contains fields BYTE (), WORD and USER-ATRB, BALD > .DAT contains the non-overlapping fields OVFL and WORD.

Then

$S < A (... -> BALU (x)) := \emptyset$

will expand as

S<A.DAT.WORD <- I.DSA

S<A.ADR.WORD <-BALU> . OVFL \* BALU> .WORD

There is no truncation for bitnames, only for bitnumbers!

#### 7.7 High Level Language Elements

Many algorithms use repetitions, conditional branches, condition dependent execution of simple or compound actions, functions and subroutines (procedures) to get economic and structured programs. Therefore special language elements have been incorporated in the HLL's and for the same reason in MIMOLA. The MIMOLA elements are: GOTO, FOR FROM BY TO WHILE DO OD, WHILE DO OD, IF THEN ELSE FI, CASE OF THEN FI ELSE ESAC, CALL, SUB, RETURN.

These elements differ in many senses from the elements in the previous chapters. The semantics are a little bit different in different languages and should not be fixed in MIMOLA to avoid a restriction of the design space. There exists no unique hardware equivalent of these elements. Thus a direct entry into the hardware data structure is impossible. The designer has to define algorithms that may replace the HLL-elements. These algorithms may use special hardware structures, designed to execute the actions of these elements, or may use the same hardware as the rest of the program. In both cases the HLL-elements can be interpreted as macros. Therefore we will treat these elements in chapter 8.5 together with suggested macro replacements.

#### 8. MACROS

#### 8.1 Use of Macros

#### 8.1.1 Standard Macros

High-level language elements, e.g. FOR FROM ..., do not generate a unique hardware replacement. These "standard macros" have to be replaced by other language elements. This can be done by the macro facility of MSS. The declaration of these macros has to be done by the programmer or the designer. The designer can experiment with different declarations and gains a great design space. Chapter 8.5 explains the standard macros in more details.

#### 8.1.2 User-Defined Macros

User-defined macros can be used as abbreviations for frequent program constructions. Thus the program text can be kept short and clear. The expansion will be defined prior to the application of the macro. ("Application" in this context means the

act of replacing a fitting program string by the declared substitute).

Another use is the introduction of new HLL constructs which are not standard. The programmer may have a certain idea of the semantics, but wants to postpone the decision on, the best implementation. Examples are synchronization primitives. Semaphore operations can be introduced by

$$\operatorname{My}$  (semaphore),  $\operatorname{Mp}$  (semaphore), monitor calls by

Monitor (entry, parameters) .

#### 8.1.3 Software and Hardware Replacements

During the design process situations may occur where it is desirable or necessary to replace certain program constructs. It may be the replacement of a complex operator module, e.g. a floating point adder, by a sequential algorithm using only simple operators. Another example is the introduction of a special hardware module instead of a software structure that is used frequently in order to increase the execution speed.

To meet these requirements, very flexible macro facilities have been implemented in MSS. Independent of standard or user defined macros nearly all possible program structures can be replaced by others.

This nowerful tool must be handled very carefully. The

#### 8.2 Macro Declarations

#### 8.2.1 Syntax

A macro declaration has the normal form

\$ MACRO

expression-1 && expression-2 && (expression-3)

ENDMACRO

The control key MACRO may be replaced by RECMACRO (see chapter 8.3).

The result of this declaration is: expression-1 will be replaced by expression-2 as often as it is found in the original program.

Expression-3 will be inserted ahead of the elementary statement block, where a replacement takes place.

expression-1 must be reducable to a nonterminal symbol except 100,101,102,105,106 (see Appendix F) by a syntax rule of the program part (see Appendix B).

expression-2 must be syntactically correct together with its context in its new place.

expression-3 must be one or more esb's. The labels of these esb's must not have more than two characters (excl."L").

expression-2 and expression-3 may use parameters that have to be introduced in expression-1. The names of these parameters are valid only inside the defining macro.

#### 8.2.2 Parameters

The range of application of a macro can be increased by parameters. In MIMOLA three different parameter types can be used in macros: macroparameters, the "?" and special labels.

#### 8.2.2.1 Macroparameters

&"name"' is a free parameter which can be used in a macro declaration. During the syntax check of the macro declaration,

If none of the four possibilities can be used to meet the syntax in the declaration, a macro parameter can be bound to a definite terminal or nonterminal, represented by its number in in Appendix F, by

&"name". <unsigned integer> This assignment will also be used during the application of a macro to a program string.

If a parameter is used several times in expression-1, the assignments must be equal. In expression-2 and expression-3, different assignments can be used. During the application the assignment.corresponding to the place of the parameter in the declaration.is valid.

```

MACRO

&arrayname.129[&index]

&arrayname/&index ->B(+)

ENDMACRO

PROGRAM

S(aa[3]) := S(bb[S(b)/R1->B(+)]),

After the macro replacement process this will be:

S(aa/3->B(+)) := S(bb/S(b)/R1->B(+)),

```

## Example 8.1

&."name"

is a special parameter for functions.

A further degree of freedom can be added to parameters by attaching

\_"name" .

"name" will be attached without blanks to the string that replaces the parameter. Examples 8.4 and 8.5 in chapter 8.5.2 show an application.

#### 8.2.2.2 Numbering of Names

"names" of elements, used in expression-2 or expression-3 of a macro declaration can be automatically varied to make a distinction between consecutive applications of the element. A "?" following a "name" (no portname!) will be replaced by a number (5 digits), built from a number (3 digits) representing the macro and a number (2 digits) that is a count of the uses of this macro. The numbers are concatenated and reversed. E.g. in the 23. application of macro no. 14,

Vn? will expand to Vn3241Ø .

Thus the digits changing most often are placed directly behind the "name".

This increases the significance of the generated names in the case of a truncation (after 8 characters at the moment) of "name"s on the right side.

#### 8.2.2.3 Special Labels

Labels as parameters cannot always be handled with macro parameters. Therefore some necessary special constructions have been included:

LaØ is the label of the current esb ,

LaDO is the label of the esb that contains

the corresponding DO of the current nesting level,

L&OD1 is the label of the esb following the esb that contains the corresponding OD of the current nesting level.

L&DO and L&OD1 can also be used in program parts and will be replaced by the fitting labels. Examples 8.5 and 8.6 show typical applications.

## 8.3 Controlled Application of Macros

# 8.3.1 RECMAC

Macros are applied during the syntax analysis process. This process sequentially scans the program string. If a macro becomes applicable to an already scanned string by a macro replacement, this cannot be detected in the same pass. By the key "RECMAC" in the declaration those macros can be marked, which shall be used in another pass. The key "ONLYRMAC" will

inhibit all macros declared with "MACRO". See e.g. example 8.8 .

# 8.3.2 Blocks

The range of macros can be controlled by nested blocking. Block delimiters are

\$ BLOCK and \$ BLOCKEND .

One global block is default without delimiters.

#### 8.3.3 Order of Macros

The application of macros is influenced by the order of their declaration.

- During the declaration of a macro Mi all prior declared matching macros, not containing esb's, are inserted into Mi.

- 2. The macros are tested in the reverse order of their declaration.

This is important if two different macros fit in the same esb before the application of the first fitting macro but not after it.

In both cases the block ranges are observed.

# 8.4 Application Rules

## 8.4.1 The Test

A macro fits a string in a program, if the syntax tree of expression-1 of the macro declaration is equivalent to the syntax tree of the string. This equivalence is tested every time a rule is applied by the syntax analyzer. The equivalence of macro parameters has been explained in

must be identical. Different attributes for equal fields are not equivalent. If a port is declared in a macro, only this port fits.

Local <u>distributors V</u> "name" (see chapter 5.4.5) will be replaced by their definition prior to the test.

# 8.4.2 The Application

In the case of a positive test, the program string is replaced by expression-2. The new esb's in expression-3 are inserted on top of the currently analyzed esb. No further test is made in the expanded parts in this pass.

<u>Labels</u> of inserted esb's are automatically numbered as in the case of a "?" (see chapter 8.2.2..2) to avoid double defined label errors. The labels of the current and the first inserted esb are exchanged. Thus the correct pointers to labels are reconstructed.

#### 8.5 Standard Macros .

The HLL elements of MIMOLA can be interpreted as macros.. The replacement is not unique and depends on the exact semantics of the element that is used in an algorithm and on the existing or proposed hardware. The given example declarations are only possible solutions. They have been included to describe the HLL elements, to give ideas for macro declarations and to serve as examples for correct macros.

#### 8.5.1 GOTO

This unconditional jump can be replaced by

\$ MACRO

GOTO &lb.115 && RP:= &lb.115

ENDMACRO

#### Example 8.3

# 8.5.2 FOR Loop

A FOR loop consists of three parts: setup, condition test and control variable updating and return.

# 8.5.2.1 Setup

A complete setup statement is

FOR a

$$\left\{ \text{FROM b} \right\}_{0}^{1} \left\{ \text{BY c} \right\}_{0}^{1} \left\{ \text{TO d} \right\}_{0}^{1}$$

$\underline{\underline{a}}$  is the control variable. It can be referenced by D(a), not by itself, to show its storage requirements.

Missing  $\underline{b}$  or  $\underline{c}$  are assumed to be 1.

Missing  $\underline{d}$  implies the ommission of the upper/lower limit test.

A macro declaration using cells in an addressable memory Sm is presented in Example 8.4. Many other possibilities exist e.g. using stacks to store the parameters. For incomplete setups, slightly varied macros must be written.

# Example 8.4

#### 8.5.2.2 Condition Test

```

The FOR loop condition test must follow the setup in another statement. The syntax is

<label> { WHILE e } DO(a)

A macro declaration fitting to example 8.4 is example 8.5.

$ MACRO

alb.115 WHILE & opw DO (&id.129) & statementblock.107;

& alb.115 IF&opw /

Sm (&id.129_0)/

Sm (&id.129_1)/

Sm (&id.129_1)/

Sm (&id.129_1) -> C (.LOOP)->B(.AND)

THEN & statementblock.107

ELSE GOTO L&OD1 FI;

```

# ENDMACRO

## Example 8.5

If different forms of setup statements exist in a program, it may be necessary to. distinguish between different forms of condition tests. In this case user defined macros for DO and OD must be used.

#### 8.5.2.3 Updating and Return

At the end of a FOR loop the control variable must be updated and a jump to the head of the loop occurs. The syntax of

## this statement is

OD(a)

In correspondence to examples 8.4 and 8.5, a macro declaration is:

```

$ MACRO

OD(&id.129)

&& Sm(&id.129_Ø):= Sm (&id.129_Ø)

/Sm(&id.129_1) ->B(+),

GOTO L&DO

ENDMACRO

```

## Example 8.6

#### 8.5.3 WHILE loop

The syntax of the WHILE loop head and tailis:

<label> WHILE < operand> DO

OD

A macro declaration is given in example 8.7.

ENDMACRO

MACRO

OD

& GOTO L&DO

ENDMACRO

# Example 8.7

#### 8.5.4 Conditions

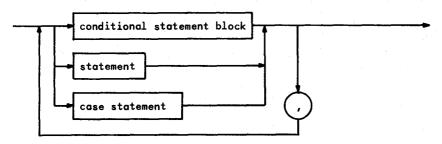

# 8.5.4.1 Conditional Statement Block

The execution of statement blocks can be condition dependend. The syntax is:

IF  THEN

$$\left\{ \text{ELSE} \quad <\text{statementblock>} \right. \right\}_{\tilde{\varphi}}^{1}$$

FI

The semantics is the same as in other HLL's. The hardware realization of conditional executions is normally a part of the control module of a computer. Therefore no generally applicable macro can be given. In our example 8.8 an IF THEN ELSE construction is split into two esb's, one executing the THEN part, the other the ELSE part. The second macro seems to be senseless, but if we observe chapter 8.3.3 we can

see that in this way the application of the first macro to already split IF THEN ELSE constructions is prevented.

# Example 8.8

#### 8.5.4.2 Conditional Operands

If the THEN and ELSE; parts of a conditional statement block differ only in one of the operands, this can be directly shown by applying the condition to the operand itself. The syntax is

Example 8.9 shows an application. The semantics and the hardware are the same for both statements.

IF S(cond) THEN R1:=  $S(a)/R2\rightarrow B(+)$ ELSE R1:=  $S(b)/R2\rightarrow B(+)$  FI

is equivalent to

R1:= S((IF S(cond) THEN a ELSE b FI))/R2->B(+)

Example 8.9 Conditional Operand

#### 8.5.4.3 Conditional Functions

The same reason as in chapter 8.5.4.2 holds for condi-

tional functions. The syntax is

<function> ::= IF <operand> THEN <function>

ELSE <function> FI

$$S(a) -> A(IF S(a) -> A(>= \emptyset)$$

THEN + ELSE - FI)

#### Example 8.10 Absolute Value of a

#### 8.5.5 CASE Statements

The CASE statement is a convenient tool to express multiple choices. The syntax is

CASE <operand> OF

ESAC

The macro of example 8.11 is a simple solution of the complex CASE statement. The generated esb's with only one case can be further expanded by another macro.

#RECMACRO CASE &op OF &cl.17¢

&& CASE &op OF

&& Lca CASE &op OF &cl.17¢ ESAC;

ENDMACRO

"THIS MACRO REDUCES CASE STATEMENTS TO CASE STATEMENTS WITH A SINGLE CASE LINE AND IS NOT SUITABLE FOR CASES INCLUDING ELSE."

Example 8.11

# 8.5.6 Subroutines

The semantics of subroutines and procedures vary strongly between different languages. Therefore only very general language elements have been incorporated in MIMOLA.

Three general actions can be distinguished: the call, the parameter handling and the return to the calling program.

CALL <identifier>

CALL ( ,

$$\{$$

$\}_{\alpha}^{*}$ )

are statements for subroutine or procedure calls without and with parameters. Possible actions are e.g. save program status, jump to subroutine head. The identifier points to the subroutine code. <operand>

is an actual parameter.

are statements that indicate necessary action at the start of the subroutine, e.g. copy the actual parameters.

<operand> is a formal parameter.

#### RETURN

is the usual statement to restore the old program status and jump back to the calling program. If values must be returned, user macros should be defined.

Subroutines are separated from other program parts by the header

SUBROUTINE <identifier>

and the tail

ENDSUB

Example 8.12 is a simple subroutine mechanism. The return address is pushed onto stack Kcall. The parameter values are pushed onto stack Kop in the calling sequence and stored in memory locations by SUB. The parameter lists must be of equal length. The example mainly demonstrates a possibility to handle calls with different numbers of parameters.

```

"WITHOUT PARAMETERS"

$MACRO CALL &id.129

RP:= &id.129,

Kcall(.PUSH):= RP -> A(.INCR)

ENDMACRO

"WITH PARAMETERS"

"SEQUENCE OF MACROS IS ESSENTIAL, BECAUSE THE LAST MACRO

CAN BE INSERTED INTO THE FIRST TWO MACROS"

SMACRO CALL &id.129 ( X )

RP:= &id.129,

Kcall(.PUSH):= RP -> A (.INCR)

ENDMACRO

CALL &id.129 ( X , &op. 113

CALL &id.129 ( X

ØMACRO

&&

Kop(.PUSH):= &op;

4.6

LCA

ENDMACRO

$MACRO CALL &id.129 (

&op.113

åå LCA

CALL &id.129 ( X

Kop(.PUSH):= &op ;

ENDMACRO

"SEQUENCE OF DECLARATION IS ESSENTIAL!"

SMACRO

SUB

2.8

х

ENDMACRO

SUB

( X , &op.113

SMACRO

( X

8.8

SUB

&op := Kop (.POP) ;

8.8

LSU

ENDMACRO

( &op.113

SHB

SMACRO

8.8

SUB

( X

( &op:= Kop(.POP) ;

8.8

LSU

ENDMACRO

$MACRO

RETURN

RP:= Kcall (.POP)