### WCET Analysis and Optimization for Multi-Core Real-Time Systems

#### Dissertation

zur Erlangung des Grades eines Doktors der Ingenieurwissenschaften

der Technischen Universität Dortmund an der Fakultät für Informatik

von

Timon Kelter

Dortmund

2015

Tag der mündlichen Prüfung: 12. März 2015

**Dekan / Dekanin:**Prof. Dr. Gernot FinkGutachter / Gutachterinnen:Prof. Dr. Peter MarwedelProf. Dr. Isabelle Puaut

## Acknowledgments

First and foremost I want to thank my advisor Prof. Dr. Peter Marwedel for pointing my research into a rewarding direction from the start on and for providing me with the opportunity to work on this fascinating field of research in an inspiring, international team. Without his continued support this thesis would not exist. I would also like to thank Prof. Dr. Isabelle Puaut for her time and commitment to review this thesis.

The implementation of the WCET analyzer and the WCET optimizations which are presented in this thesis would not have been possible without the previous work of numerous colleagues at our chair over the course of more than one decade. I am especially grateful for the provision of the WCC framework, on which the majority of my practical work was built. In this context, I owe special thanks to Prof. Dr. Heiko Falk for being one of the most thorough reviewers and advisors I have ever met, to Dr. Paul Lokuciejewski for introducing me to this interesting field of research, to Dr. Sascha Plazar for being a fantastic office neighbor, to Jan Christopher Kleinsorge for our mutual motivation to finish the PhD project and to all of them for the enjoyable time in countless on- and off-topic disucssions.

For proof-reading my drafts and papers, for helpful discussions and for being really good colleagues I would also like to thank Björn Bönninghoff, Olaf Neugebauer, Pascal Libuschewski, Chen-Wei Huang, Dr. Michael Engel, Helena Kotthaus, Andreas Heinig, Florian Schmoll and Dr. Daniel Cordes. On the implementation side, my work was supported by Jan Körtner, Hendrik Borghorst, Tim Harde, Christian Günter and Henning Garus. Without their help the whole WCET analyzer implementation would be in a different shape now.

Furthermore, I am deeply thankful towards the former WCET analysis team at the National University of Singapore, most of all to Dr. Sudipta Chattopadhyay and Prof. Dr. Abhik Roychoudhury, for giving me the opportunity to work on the Chronos WCET analyzer. Without these first steps I possibly would have not found my way into the topic of WCET analysis.

What has kept me going in the last years was of course not only scientific progress but also the support that I received from friends and family, who kept me grounded when my thoughts were spinning around work issues. Many thanks to all of you – you know who you are. In particular I owe my father a big debt of gratitude for motivating me to pick up computer science as a profession and to finally strive for the PhD.

## Abstract

During the design of safety-critical real-time systems, developers must be able to verify that a system shows a timely reaction to external events. To achieve this, the Worst-Case Execution Time (WCET) of each task in such a system must be determined. The WCET is used in the schedulability analysis in order to verify that all tasks will meet their deadlines and to verify the overall timing of the system. Unfortunately, the execution time of a task depends on the task's input values, the initial system state, the preemptions due to tasks executing on the same core and on the interference due to tasks executing in parallel on other cores. These dependencies render it close to impossible to cover every feasible timing behavior in measurements. It is preferable to create a static analysis which determines the WCET based on a safe mathematical model.

The static WCET analysis tools which are currently available are restricted to a single task running uninterruptedly on a single-core system. There are also extensions of these tools which can capture the effects of multi-tasking, i.e., preemptions by higher-priority tasks, on the WCET for certain well-defined scenarios. These tools are nowadays already used to verify industrial real-time software, e.g., in the automotive and avionics domain. Up to now, there are no mature tools which can handle the case of parallel tasks on a multi-core platform, where the tasks potentially interfere with each other.

This dissertation presents multiple approaches towards a WCET analysis for different types of multi-core systems. They are based upon previous work on the modeling of hardware and program behavior but extend it to the treatment of shared resources like shared caches and shared buses. We present multiple methods of integrating shared bus analysis into the classical WCET analysis framework and show that time-triggered bus arbitration policies can be efficiently analyzed with high precision. In order to get precise WCET estimations for the case of shared caches, we present an efficient analysis of interactions in parallel systems which utilizes timing information to cut down the search space. All of the analyses were implemented in a research C compiler. Extensive evaluations on real-time benchmarks show that they are up to 11.96 times more precise than previous approaches.

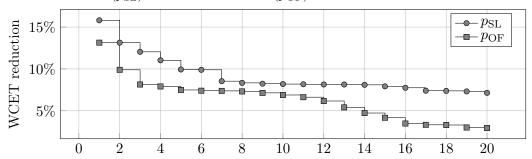

Finally, we present two compiler optimizations which are tailored towards the optimization of the WCET of tasks in multi-core systems, namely an evolutionary optimization of shared resource schedules and an instruction scheduling which uses WCET analysis results to optimally place shared resource requests of individual tasks. Experiments show that the two combined optimizations are able to achieve an average WCET reduction of 33%.

During the course of this thesis, a complete WCET analysis framework was developed which can be used for further work like the integration of multi-task and multi-core-aware techniques into a single analyzer.

### **Publications**

Parts of this thesis have been published in journals and the proceedings of the following conferences and workshops (in chronological order):

- Timon Kelter, Heiko Falk, Peter Marwedel, Sudipta Chattopadhyay, and Abhik Roychoudhury. "Bus-Aware Multicore WCET Analysis through TDMA Offset Bounds". In: *Proceedings of the 23rd Euromicro Conference on Real-Time Systems (ECRTS)*. Porto, Portugal, 07/2011, pp. 3–12.

- Sudipta Chattopadhyay, Chong Lee Kee, Abhik Roychoudhury, Timon Kelter, Heiko Falk, and Peter Marwedel. "A Unified WCET Analysis Framework for Multi-Core Platforms". In: *IEEE Real-Time and Embedded Technology and Applications Symposium (RTAS)*. Beijing, China, 04/2012, pp. 99–108.

- Timon Kelter, Tim Harde, Peter Marwedel, and Heiko Falk. "Evaluation of Resource Arbitration Methods for Multi-Core Real-Time Systems". In: *Proceedings of the 13th International Workshop on Worst-Case Execution Time Analysis (WCET)*. Ed. by Claire Maiza. Paris, France, 07/2013.

- Timon Kelter, Heiko Falk, Peter Marwedel, Sudipta Chattopadhyay, and Abhik Roychoudhury. "Static Analysis of Multi-Core TDMA Resource Arbitration Delays". English. In: Real-Time Systems 50.2 (03/2014), pp. 185–229. ISSN: 0922-6443. DOI: 10.1007/s11241-013-9189-x. URL: http://dx.doi.org/10.1007/s11241-013-9189-x.

- Sudipta Chattopadhyay, Lee Kee Chong, Abhik Roychoudhury, Timon Kelter, Peter Marwedel, and Heiko Falk. "A Unified WCET Analysis Framework for Multicore Platforms". In: *ACM Transactions on Embedded Computing Systems* 13.4s (04/2014), 124:1–124:29. ISSN: 1539-9087. DOI: 10.1145/2584654. URL: http://doi.acm.org/10.1145/2584654.

- Timon Kelter, Peter Marwedel, and Hendrik Borghorst. "WCET-aware Scheduling Optimizations for Multi-Core Real-Time Systems". In: International Conference on Embedded Computer Systems: Architectures, Modeling, and Simulation (SAMOS). Samos, Greece, 07/2014.

- Chen-Wei Huang, Timon Kelter, Bjoern Boenninghoff, Jan Kleinsorge, Michael Engel, Peter Marwedel, and Shiao-Li Tsao. "Static WCET Analysis of the H.264/AVC Decoder Exploiting Coding Information". In: *International Conference on Embedded and Real-Time Computing Systems and Applications (RTCSA)*. IEEE. Chongqing, China, 08/2014.

- Timon Kelter and Peter Marwedel. "Parallelism Analysis: Precise WCET Values for Complex Multi-Core Systems". In: *Third International Workshop on Formal Techniques for Safety-Critical Systems (FTSCS)*. Ed. by Cyrille Artho and Peter Ölveczky. Luxembourg: Springer, 11/2014.

# Contents

| 1 | Inti | roduction                                                     | 1  |  |  |  |  |

|---|------|---------------------------------------------------------------|----|--|--|--|--|

|   | 1.1  | Motivation                                                    | 3  |  |  |  |  |

|   | 1.2  | Contributions of this Work                                    | 7  |  |  |  |  |

|   | 1.3  | Organization of the Thesis                                    | 8  |  |  |  |  |

|   | 1.4  | Author's Contribution to this Dissertation                    | 9  |  |  |  |  |

| 2 | Tin  | ning Analysis Concepts                                        | 11 |  |  |  |  |

|   | 2.1  | Abstract Interpretation                                       | 12 |  |  |  |  |

|   | 2.2  | WCET Analysis for Uninterrupted Single Tasks                  | 18 |  |  |  |  |

|   |      | 2.2.1 Static WCET Analysis                                    | 19 |  |  |  |  |

|   |      | 2.2.2 Parametric WCET analysis                                | 21 |  |  |  |  |

|   |      | 2.2.3 Hybrid WCET analysis                                    | 21 |  |  |  |  |

|   |      | 2.2.4 Early-Stage WCET analysis                               | 22 |  |  |  |  |

|   |      | 2.2.5 Statistical WCET analysis                               | 22 |  |  |  |  |

|   |      | 2.2.6 WCET-friendly Hardware Design                           | 23 |  |  |  |  |

|   |      | 2.2.7 Experiences with Practical Application of WCET Analysis | 23 |  |  |  |  |

|   |      | 2.2.8 Timing Anomalies                                        | 24 |  |  |  |  |

|   |      | 2.2.9 Compositionality in WCET Analysis                       | 27 |  |  |  |  |

|   | 2.3  | Timing Analysis of Sequential Multi-Task Systems              | 29 |  |  |  |  |

|   |      | 2.3.1 Accounting for the Timing Behavior of System Calls      | 29 |  |  |  |  |

|   |      | 2.3.2 Accounting for Task Interaction Impacts on the WCET .   | 30 |  |  |  |  |

|   |      | 2.3.3 Schedulability of Multi-Task Systems with Given WCETs   | 32 |  |  |  |  |

|   | 2.4  | 4 Timing Analysis of Parallel Multi-Task Systems              |    |  |  |  |  |

|   |      | 2.4.1 Multi-Core Systems                                      | 33 |  |  |  |  |

|   |      | 2.4.2 Distributed Systems                                     | 34 |  |  |  |  |

| 3 | wc   | CC Framework                                                  | 37 |  |  |  |  |

|   | 3.1  | Related Work                                                  | 38 |  |  |  |  |

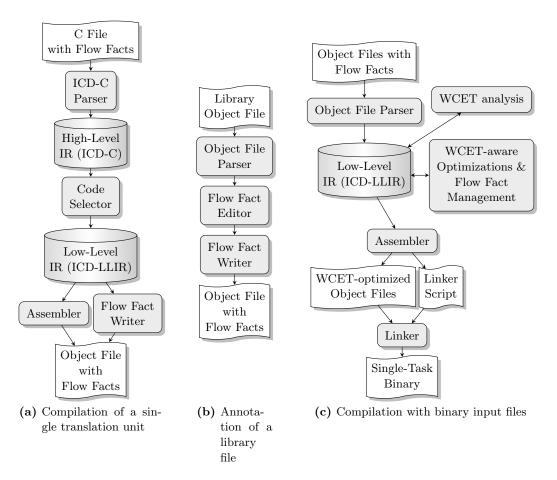

|   | 3.2  | Compiler Phases                                               | 39 |  |  |  |  |

|   | 3.3  | Flow Fact Management                                          | 41 |  |  |  |  |

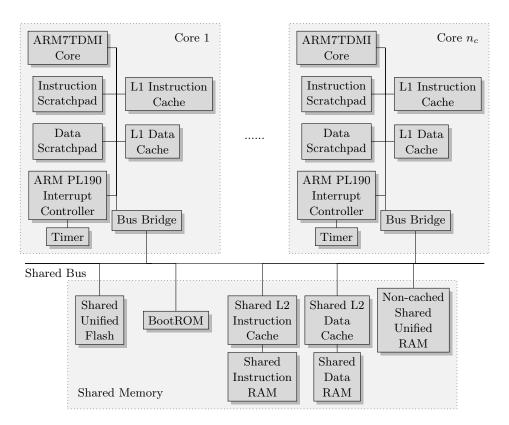

|   | 3.4  | System Model                                                  | 43 |  |  |  |  |

|   | 3.5  | Extensions for Binary Input Files                             | 47 |  |  |  |  |

| 4 | Sin  | gle-Core WCET-Analysis                                        | 51 |  |  |  |  |

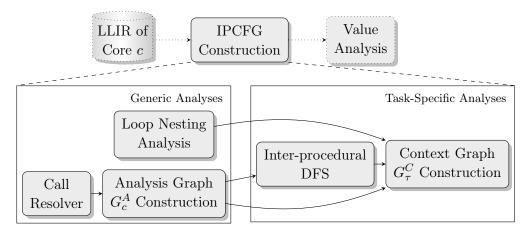

|   | 4.1  | IPCFG Construction                                            | 52 |  |  |  |  |

|   |      | 4.1.1 Analysis Graph                                          | 54 |  |  |  |  |

|   |      | 4.1.2 Context Graph                                           | 55 |  |  |  |  |

|   | 4.2  | Value Analysis                                                | 60 |  |  |  |  |

|   |      | 4.2.1 Abstract Value Domain                                   | 60 |  |  |  |  |

Contents

|   |     | 4.2.2  | Challenges of Predicated Execution            | 65  |

|---|-----|--------|-----------------------------------------------|-----|

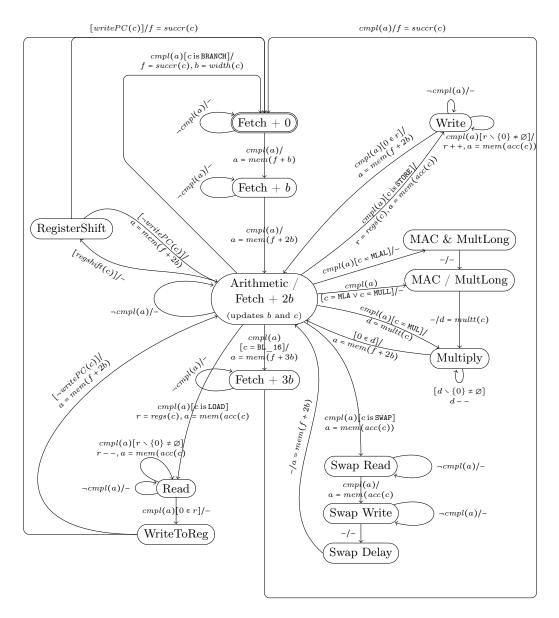

|   | 4.3 | Micro  | parchitectural Analysis                       | 6   |

|   |     | 4.3.1  | ARM7TDMI Pipeline Model                       | 6   |

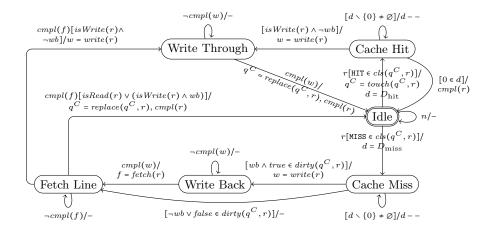

|   |     | 4.3.2  | Cache Analysis                                | 70  |

|   | 4.4 | Path   | Analysis                                      | 73  |

|   | 4.5 | Evalu  | nation                                        | 70  |

| 5 | Mu  | lti-Co | re WCET Analysis                              | 8:  |

|   | 5.1 |        | duction                                       | 85  |

|   | 5.2 |        | -Core Challenges                              | 85  |

|   |     | 5.2.1  | Shared Caches                                 | 85  |

|   |     | 5.2.2  | Shared Interconnection Structures             | 8   |

|   | 5.3 | Relate | ed Work                                       | 80  |

|   |     | 5.3.1  | WCET Analysis Approaches for Multi-Cores      | 80  |

|   |     | 5.3.2  | WCET-friendly Multi-Core Architecture Design  | 89  |

|   | 5.4 |        | tioned Multi-Core WCET Analysis               | 90  |

|   | 0.1 | 5.4.1  | Shared Cache Handling                         | 9   |

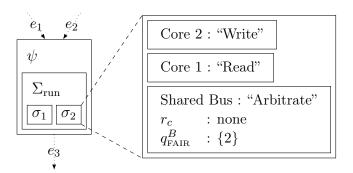

|   |     | 5.4.2  | Shared Bus Analysis Preliminaries             | 94  |

|   |     | 5.4.3  | Basic Bus Domains                             | 9   |

|   |     | 5.4.4  | Loop Unrolling                                | 100 |

|   |     | 5.4.5  | Offset Contexts                               | 10  |

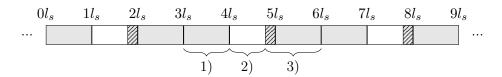

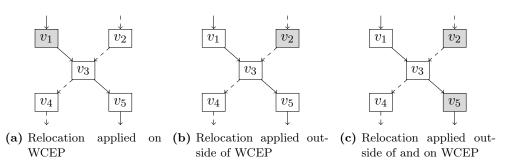

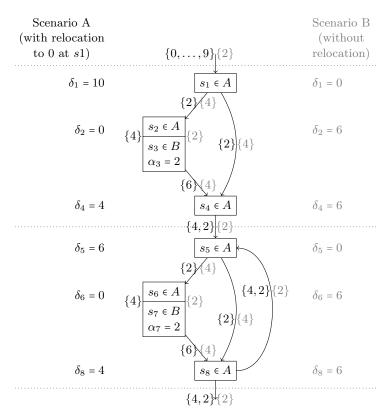

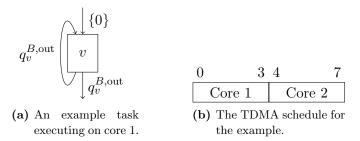

|   |     | 5.4.6  | Offset Relocation                             | 104 |

|   |     | 5.4.7  | Timing-Anomaly-Free Analysis                  | 110 |

|   |     | 5.4.8  | Evaluation                                    | 113 |

|   | 5.5 |        | ed WCET Analysis for Complex Multi-Cores      | 12  |

|   |     | 5.5.1  | Related Work                                  | 120 |

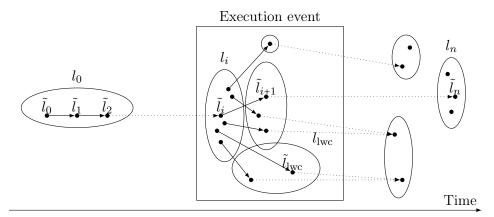

|   |     | 5.5.2  | Task Model                                    | 123 |

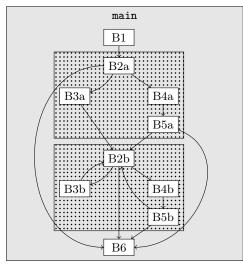

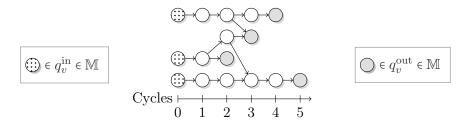

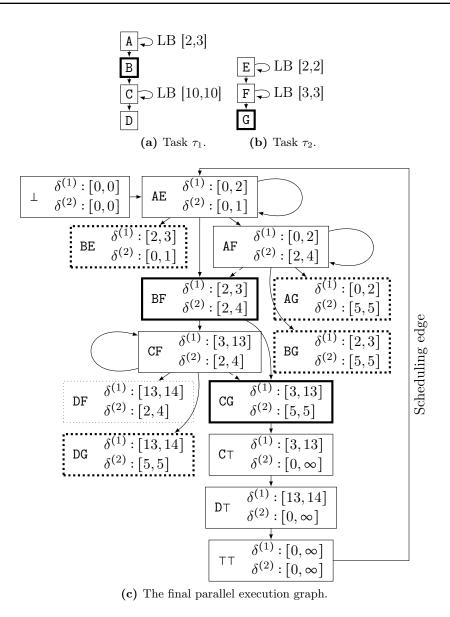

|   |     | 5.5.3  | Motivating Example                            | 123 |

|   |     | 5.5.4  | Prerequisites                                 | 120 |

|   |     | 5.5.5  | Parallel Execution Graph Construction         | 12  |

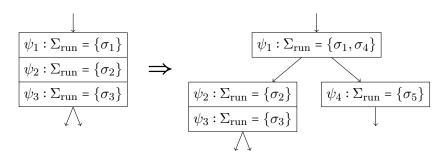

|   |     | 5.5.6  | Parallel System States                        | 13  |

|   |     | 5.5.7  | Correctness                                   | 13  |

|   |     | 5.5.8  | Extensions                                    | 138 |

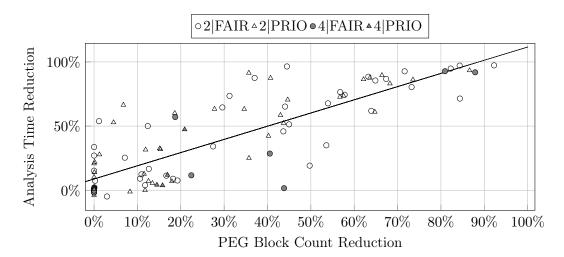

|   |     | 5.5.9  | Evaluation                                    | 140 |

|   | 5.6 | Sumn   | nary                                          | 14  |

| 6 | Mu  | lti-Co | re WCET Optimization                          | 14' |

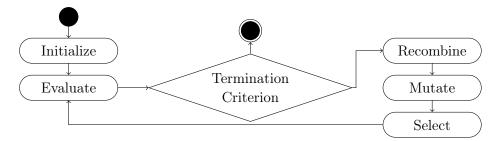

|   | 6.1 |        | -Objective Evolutionary Schedule Optimization | 14  |

|   |     | 6.1.1  | Related Work                                  | 14  |

|   |     | 6.1.2  | Evolutionary Algorithm                        | 14  |

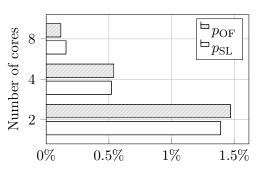

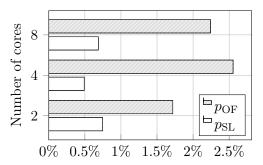

|   |     | 6.1.3  | Evaluation                                    | 15  |

|   | 6.2 |        | T-driven Multi-Core Instruction Scheduling    | 15  |

|   |     |        | Related Work                                  | 15  |

| xi |

|----|

|    |

|              |                        | 6.2.2 Scheduling Heuristics | 150 |

|--------------|------------------------|-----------------------------|-----|

|              |                        | 6.2.3 Evaluation            | 15  |

|              | 6.3                    | Summary                     | 16  |

| 7            | Cor                    | nclusion and Future Work    | 16  |

|              | 7.1                    | Summary                     | 16  |

|              | 7.2                    | Future Work                 | 16  |

| Li           | ${f st}$ of            | Figures                     | 169 |

| Li           | $\operatorname{st}$ of | Tables                      | 169 |

| Li           | st of                  | Algorithms                  | 17  |

| $\mathbf{G}$ | lossa                  | ry                          | 17  |

| B            | ibliog                 | graphy                      | 17  |

| $\mathbf{A}$ | Em                     | ployed Benchmarks           | 209 |

### Introduction

This dissertation deals with an aspect of computer science that has been a secondclass citizen since the emergence of the discipline: With *time*. Or, to put it more precisely, with *safe bounds on the timing behavior* of programs running on a computer system.

Since the days of mainframes, attempts have been made to increase the productivity of a programmer by supplying him with ever more powerful programming languages and compilers for the latter [Myc07], by teaching useful idioms and patterns [GHJ+95] and by making the single computers faster to allow the software complexity to increase steadily [Sch97]. The runtime behavior of algorithms has traditionally been classified asymptotically in big O notation which eases or even enables the reasoning about runtime behavior for complex algorithms [Weg03]. For many computer applications the asymptotical classification is sufficient, even though its limitations are already stressed by examples like the Simplex algorithm, which in spite of having exponential asymptotical runtime performs better than its polynomial-time counterparts on most real-world examples [Cor10, Choosing an optimizer for your LP problem].

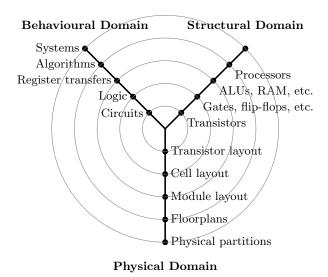

The major shortcoming of this type of runtime classification is that it is not usable in the important area of real-time systems, i.e., computer systems in which the executed tasks must always fulfill their work in a bounded time interval or before a given deadline. An asymptotic modeling which ignores constant factors in the runtime formula is not applicable here, since taking twice the allowed time or only once is an important difference, possibly rendering the system dysfunctional in the former case. Most real-time systems are also embedded systems, i.e., "information processing systems embedded into enclosing products" [Mar11], which are integrated into many devices of daily life. Application domains for embedded systems are numerous and cover areas like automotive electronics, avionics, railways, telecommunication, the health sector, security, consumer-electronics, fabrication equipment, smart buildings, logistics, robotics, military applications, and many more [Mar11].

Real-time systems are generally classified as *soft* or *hard* real-time systems, where "soft" means that deadlines may be violated for *a few* executions of a task, but not regularly and "hard" means that not a single deadline must be violated. Multimedia applications like audio and video decoders are prime examples for soft real-time systems, whereas industrial *Electronic Control Units* (ECU) in robotics, power stations, cars and planes are typical hard-real time systems. Modern cars for example have more than 70 ECUs [ES08] for engine control, safety features like anti-lock braking

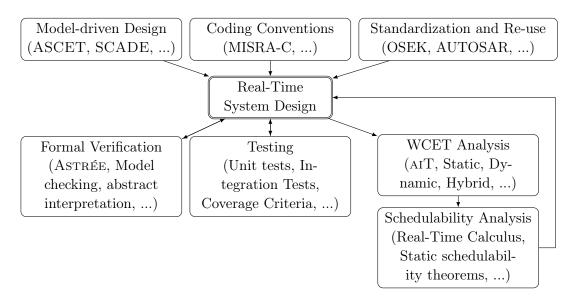

Figure 1.1: Real-time system verification tools.

and electronic stability program and multi-media functions. At least for the first two categories, hard-real time implementations clearly must be provided to ensure a timely reaction of the system. According to a recent market study, about 60% of all embedded development projects [BW13] require real-time capabilities, though in some of these cases soft-real time may be sufficient. Still, the rising number of complications with real-world safety-critical embedded systems of everyday life, mostly cars<sup>1</sup>, demonstrates that (semi-)automated safety certification of embedded systems is highly desirable. Here, WCET analysis comes into play, as a means to semi-automatically verify the timing behavior of the task set under analysis. Of course, this has to be complemented by other analyses as sketched in Figure 1.1.

The upper half of the figure shows methodologies, coding conventions and standard components which are used to avoid programming errors and to increase the productivity. They have a direct influence on the shape of the final real-time system code. As an example, code generation from models and conventions like MISRA-C [MIS13] can ease the WCET analysis by limiting the variability of the code and prohibiting hard-to-analyze software constructions.

The lower half of Figure 1.1 shows tools which are used to verify a system that has already been partly or fully designed. Formal verification is needed to detect run-time errors like, e.g., null-pointer, overflow, out-of-bounds bugs. One of the best-known tools in this area is ASTRÉE<sup>2</sup> [Abs14b] which similar to WCET analysis relies on abstract interpretation to derive static information about the program. Model-checking has also proven to be useful especially when a system implementation is already generated from a high-level model. Model checkers focus on proving the

<sup>&</sup>lt;sup>1</sup>As an example, there were 24 retractions of vehicle classes in the year 2011 [Ele12].

<sup>&</sup>lt;sup>2</sup>Here and throughout the rest of this thesis, example tools are set in small caps.

1.1. Motivation 3

absence of deadlocks, reachability conditions and program termination, rather than on run-time errors in real code. Testing is mandatory for any type of development, with a wealth of testing frameworks and methodologies being available and widely used.

WCET and schedulability analysis are then providing what formal error-checking and testing alone cannot offer, namely safe and precise bounds on the runtime of individual tasks (WCET analysis) and statements on whether the given task set will always meet its deadline on the given platform (Schedulability analysis). AIT [Abs14a] is the de-facto standard for industrially used WCET analysis. In addition to delivering highly precise WCET values for single tasks, it can also compute the worst-case memory consumption of tasks.

Therefore, WCET analysis is one of the key elements in timing verification. With imprecise, or worse with unsafe WCET values all statements derived in the schedulability analysis are overly pessimistic or even void.

#### 1.1 Motivation

Unfortunately, a precise WCET analysis is undecidable in general. This is easy to see, since the WCET analysis problem is just an extension of the halting problem, where we not only ask whether a program will terminate, but also when it will terminate. Since the halting problem is undecidable [Weg99], so is the WCET analysis problem<sup>3</sup>. In addition, the timing behavior of modern hardware shows enough variance to render a simple enumeration of all possible execution paths infeasible.

Therefore, any practically feasible WCET analysis has to use approximation as a means to make the problem decidable at all. We will see in Chapter 2 that even with algorithmic approximation, WCET analysis potentially still requires some user interaction for complex tasks.

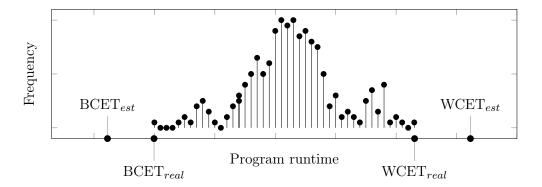

Since WCET analysis in general requires approximation, we distinguish between the WCET<sub>real</sub>, which is the true worst-case runtime of the task under analysis, and estimations WCET<sub>est</sub>  $\geq$  WCET<sub>real</sub>. In Figure 1.2 an example distribution of runtimes is given, where the WCET<sub>real</sub> is marked along with with one possible example of a WCET<sub>est</sub> for this task. It is worth noticing that for any real task a runtime distribution as shown in Figure 1.2 can hardly be constructed, since it needs to cover all input combinations and all possible initial system states. Similar to the WCET we can also define the Best-Case Execution Time (BCET) of a task which is also indicated in Figure 1.2, where we again distinguish between the BCET<sub>real</sub> and the BCET<sub>est</sub>  $\leq$  BCET<sub>real</sub>. The BCET is also important in the timing analysis, to, e.g., derive minimum task inter-arrival times in the schedulability analysis, but

<sup>&</sup>lt;sup>3</sup>Even though Kirner, Zimmermann and Richter argue that the halting problem is in fact *not* undecidable for existing bounded-memory platforms [KZR09], it still is orders of magnitude too complex to decide in reasonable time.

**Figure 1.2:** A sample distribution of runtimes of a program, along with with sample BCET and WCET estimates.

since most WCET analysis concepts are also directly applicable to BCET analysis, we focus on the WCET side in the following. Nevertheless, most analyses from Chapter 4 and Chapter 5 yield both BCET and WCET values. Since the WCET $_{real}$  is unknown in general, we use the term "WCET" as a synonym for "WCET $_{est}$ " throughout this thesis (same for BCET).

Any WCET analysis is required to be safe, i.e., the relation WCET $_{est} \geq$  WCET $_{real}$  must always hold. In addition, it is desirable for the analysis to be precise, which means that the difference WCET $_{est}$  – WCET $_{real}$  should be minimized. To the best of the author's knowledge, theoretical bounds on the precision of WCET analyses are not available, so the precision is usually determined empirically by comparing the WCET $_{est}$  with measured execution times.

For a task which runs uninterruptedly on a single core, effective WCET analysis methodologies were developed and compared throughout the last two decades, which deliver WCET estimates which are 3% to 25% above the WCET<sub>real</sub> [Abs14a]. One key problem for these analyses is that preemptions by other tasks are usually not accounted for in the WCET analysis itself, but only during schedulability analysis (cf. Figure 1.1). This decomposition of WCET and schedulability eases the analysis of both, but also promotes overestimation, since the communication between WCET and schedulability analysis is unidirectional and on a very coarse level. Most importantly, the schedulability analysis intentionally has no access to the detailed worst-case hardware states that are generated by the WCET analysis. Instead, the schedulability tests are solely based on numeric WCET values and platform assumptions to lower their algorithmic complexity.

WCET analysis faces an equally important problem due to the latest hardware development trends, namely the shift towards multi-core architectures. While until 2005 the performance improvement of new chips mainly was generated by frequency increases, we are now faced with stagnating frequencies and rising numbers of cores per chip [Sut12]. This can be seen as a general trend towards parallel computing which does not stop at homogeneous multi-cores, but continues with heterogeneous

1.1. Motivation 5

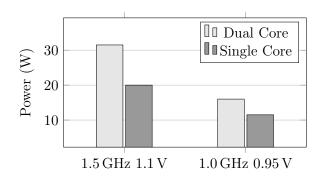

**Figure 1.3:** Multi-core implementation power consumption for the FreeScale MPC8641 [Fre09, Section 1.1], depending on the core frequency and voltage.

multi-cores (since 2009) and "elastic cloud compute cores" (since 2010), e.g., the outsourcing of computations to commercial or private clouds. While the latter is not expected to have a big impact on hard real-time systems, multi-cores have already arrived in the embedded market.

As Equation 1.1 shows, the power consumption of a core is directly proportional to the frequency, but according to [Fre09] increased voltages are needed to reach higher frequencies due to electrotechnical reasons. Therefore, by rule of thumb, a doubling of frequencies leads to a fourfold increase in power consumption [Fre09].

Power

$$\propto$$

Capacitance  $\times$  Voltage<sup>2</sup>  $\times$  Frequency (1.1)

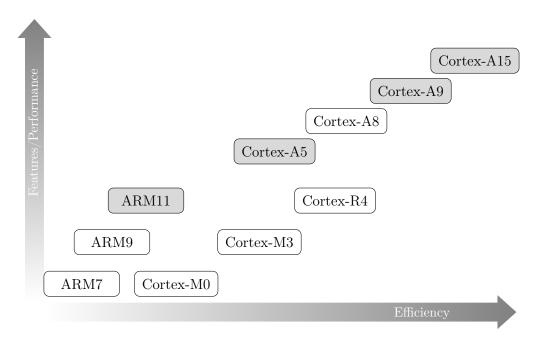

This power consumption increase in turn generates more heat which leads to decreased component lifetime and higher cooling needs. For battery-driven devices like many embedded systems all of these points are highly important and motivate the now widespread use of multi-cores also in the embedded domain. As an example, Figure 1.3 shows the power consumption of the FreeScale MPC8641 in singleand dual-core configurations as found in [Fre09]. It is visible that the dual-core configuration only needs about 30% more power than the single-core one, whereas a single-core implementation with doubled frequency would have caused an four-fold increase of the power demand as mentioned above. A more extreme example is the IBM SyNAPSE chip, according to IBM research the biggest chip that was ever built by IBM, which integrates 4096 cores on a single chip [Joh14]. Each core is running at 1 kHz only, leading to a marginal power consumption of 70 mW. Though this chip is not yet in volume production, it shows the capabilities of multi-cores. Finally, Figure 1.4 presents recent ARM architectures which can be found in abundance in modern smartphones and embedded systems. It is visible that high-performance (with the exception of the Cortex-A8) is only achieved with multi-core designs, especially since these chips are often used in passively cooled systems where the heating problem mentioned above is a severe issue. For the ARM designs and similar chips which are intended to offer more than some kilohertz of per-core frequency it is

**Figure 1.4:** ARM Processor Families [ARM14b]. Multi-core architectures are marked in gray.

already predicted that the multi-core scaling will finally end due to thermal issues which arise when all cores on the same chip are powered on [EBS+11]. This effect is also called "dark silicon", since it implies that not all cores can be powered on at the same time without causing the system to overheat. Therefore, even though the integration density may still increase the number of concurrently usable cores does not, because some of them must be powered off, i.e., they are "dark silicon". Nevertheless, multi-cores will continue to scale for some time and will remain the predominant type of computing system for the foreseeable future.

From the WCET perspective, the problem with this inevitable trend is that the cores in a multi-core system usually share some hardware components for efficiency reasons. Typical examples of this are shared I/O-devices, shared main memory and shared cache levels. Since these resources can only be accessed by one task at a time, concurrent requests to the resource need to be sequentialized by some kind of arbiter. This arbitration delay now has to be bounded as precisely as possible by the static WCET analysis, which may be hard to achieve, depending on the employed arbitration strategy. In addition, some shared components have a shared state which determines the timing behavior of the component. A prime example for this is a shared cache where it makes a big difference in terms of timing whether the requested block was found in the cache or not. Therefore WCET analysis now faces the problem of finding static estimates of

- 1. the arbitration delay and

- 2. the shared state

of any shared resource, or to put it in other words, the *interference* on this resource. Both may depend on the *order of concurrent accesses* which are issued to the resource. As an example, a shared cache will have a different state if two conflicting cache blocks A and B are requested in the order A, B, A, B or B, B, A, A. Mature WCET analysis tools for multi-cores are not yet available, therefore the alarming reaction of industrial real-time system designers is to switch all but one single core off [WHK+13]. This removes all interference-related problems, but of course also effectively degrades the multi-core system to a single-core one. Since the most recent hardware generation is often only available as multi-core chips, this is sometimes still the only viable option.

#### 1.2 Contributions of this Work

This thesis presents multiple approaches towards a precise WCET analysis for multicores, which may help to alleviate the aforementioned problems with the adoption of multi-core hardware in real-time system design. Also, the concrete implementation of these approaches inside the WCET-aware C Compiler (WCC) is demonstrated and used to evaluate the presented techniques. The WCC also provides unique opportunities to couple the analysis of a task's WCET with the optimization of the latter. Therefore, this thesis also presents two optimizations which utilize this unique capability to demonstrate that an optimization of task WCETs is feasible and useful in practice.

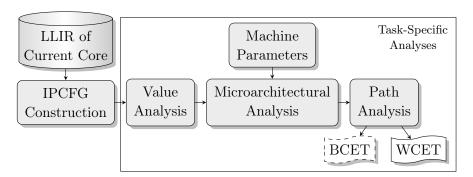

We build our approach on the branch of WCET analysis methods which has proven to be most efficient in the past, namely on a decomposition of the WCET analysis into microarchitectural analysis and path analysis. This approach is also employed in the de-facto standard WCET analyzer AIT [Abs14a]. It consists of an abstract interpretation-based microarchitectural analysis phase, during which the best- and worst-case runtime of each basic block in the task's control-flow graph is determined. With these values a successive path analysis can compute the shortest and longest path through the control-flow graph, whose length corresponds to the BCET and WCET, respectively.

For the single-core case, the WCET analysis methodology is reviewed. Focus is laid on how to achieve a value analysis with sufficient precision and on the modeling of microarchitectural features, since these form the basis for a precise WCET analysis of both single- and multi-core systems.

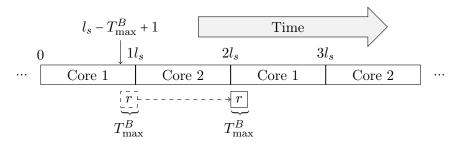

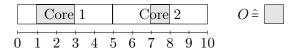

The extension of the microarchitectural modeling to include shared buses and shared caches is discussed, and the possibility to model the behavior of time-triggered arbiters by means of *TDMA offsets* is presented. These can be used to statically capture the duration of shared resource access requests. Their true potential only unfolds when they are not applied naively, but combined with intelligent loop unrolling techniques. Since the loop unrolling incurs a significant analysis time

overhead, the concepts of offset relocation and offset contexts are established to allow for a fast but also precise WCET analysis.

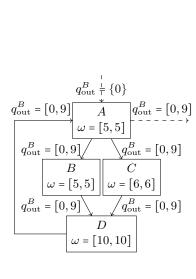

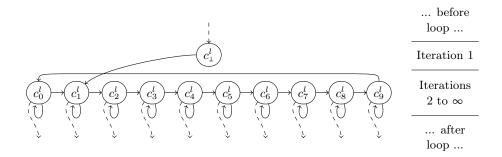

The timing behavior of stateful resources and non-time-triggered arbiters relies on the *ordering* of accesses, therefore any analysis which tries to bound this timing must safely consider all possible interleavings of potentially parallel actions. This thesis for the first time presents a structured way to explore such interleavings on the single-machine-cycle level. To avoid some part of the combinatorial explosion that is inevitable in such analyses, a timing-based pruning criterion is developed which uses the generated timing information to rule out invalid parallel system states.

The presented analysis methods are compared with respect to the achievable precision and to the overhead which is incurred by platform configurations which are routinely advertised for being more predictable and thus easier to analyze.

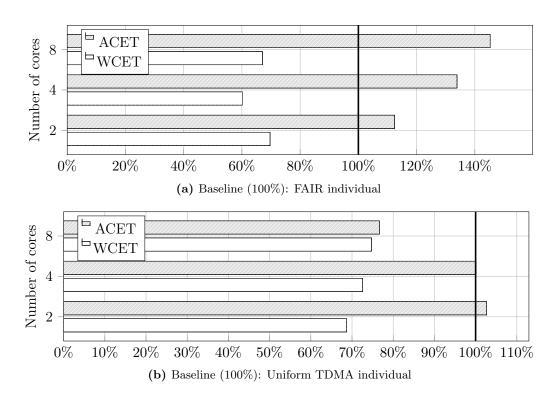

Finally, two compiler optimizations are given, which can be used to decrease the WCET of tasks in a multi-core system. The first is a WCET-aware multi-criteria evolutionary optimization of the schedule of shared resources. By efficiently exploring different system configurations a suitable schedule can be found for a given task set. It is also shown that this schedule is highly dependent on the given tasks, i.e., an optimal default schedule cannot be specified in general, necessitating an optimization like the one presented here.

The second optimization is a WCET-driven instruction scheduling which utilizes the close coupling of analyses and optimizations inside the WCC by using microarchitectural analysis results to optimally place single instructions inside the tasks' source code. The placement is done in such a way that the single shared resource accesses incur minimum access overhead, which is only possible with the help of detailed microarchitectural information.

#### 1.3 Organization of the Thesis

The structure of the remaining parts of this thesis is as follows:

- Chapter 2 presents the existing concepts used in WCET analysis. It starts with a general review of abstract interpretation, the basic method onto which the presented WCET analysis is built. Subsequently, different approaches to WCET analysis are shown, and necessary definitions of WCET-related phenomena like timing compositionality and timing anomalies are given. The chapter closes with a presentation of preexisting approaches to WCET analysis in multi-task and multi-core systems.

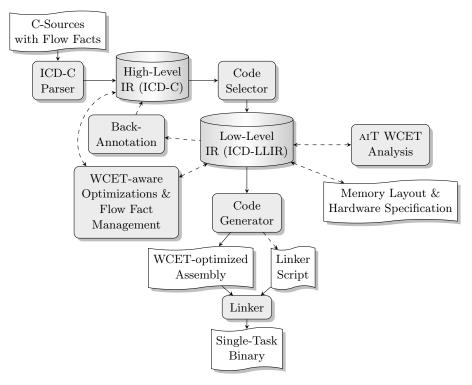

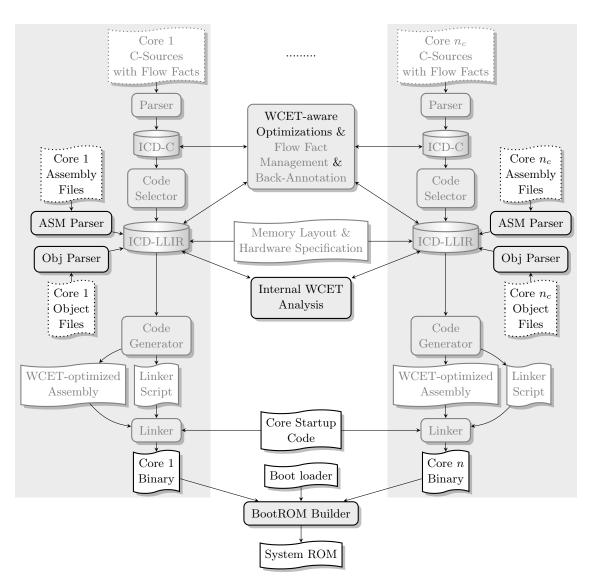

- The WCC framework is introduced in **Chapter 3**. Starting with an overview of the compiler infrastructure and related work on similar projects, it covers the assumed system model and the compiler phases. Finally, extensions of the WCC framework to incorporate binary code into WCET analysis and optimization are presented.

- Chapter 4 picks up the WCET analysis concepts presented in Chapter 2 and demonstrates how these are used in the context of the WCC framework to create a WCET (and BCET) analyzer for a single-core ARM platform.

- The main contributions of this thesis are found in **Chapter 5**, where the methods for WCET analysis in multi-core systems are discussed. It covers TDMA offset analysis for time-triggered arbiters as well as precise analysis for less predictable architectures and an extensive evaluation.

- Chapter 6 contains the presentation of the aforementioned two compiler optimizations tailored towards WCET optimization. It starts with the evolutionary shared resource schedule optimizations and then proceeds with the WCET-aware multi-core instruction scheduler. For both optimizations, evaluation results on a large number of real-time benchmarks are given.

- Finally, **Chapter 7** closes the thesis with a summary and an outlook on future work.

#### 1.4 Author's Contribution to this Dissertation

According to §10(2) of the "Promotionsordung der Fakultät für Informatik der Technischen Universität Dortmund vom 29. August 2011", a dissertation within the context of doctoral studies has to contain a separate list that highlights the author's contributions to research and results obtained in cooperation with other researchers. Therefore, the following overview lists the contribution of the author on the presented results for each chapter:

- Chapter 2: This chapter summarizes related work only, therefore there is no contribution to account for.

- Chapter 3: The WCC framework [FL10] was created by a multitude of people, among others Heiko Falk, Paul Lokuciejewski, Sascha Plazar and Jan Kleinsorge. The author has also worked on this framework to some extent by using it as a basis for the multi-core WCET analysis and optimizations. The extension of the WCC framework to multi-core architectures was done by the author only. An initial version of the virtual platform that was used to evaluate the proposed architecture was implemented by Tim Harde [Har13] and later largely re-structured by the author. The employed cycle-true virtual platform simulator CoMET was donated by Synopsys Inc. [Syn14].

- The concepts for the extension of the WCC towards the handling of binary input files were developed by the author and implemented by Christian Günter [Gün13].

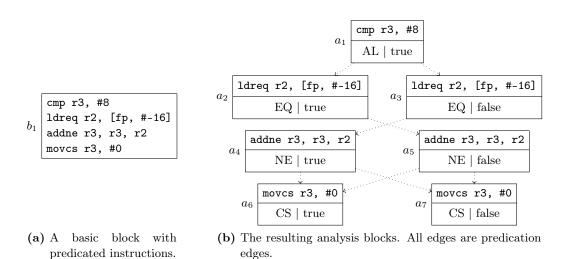

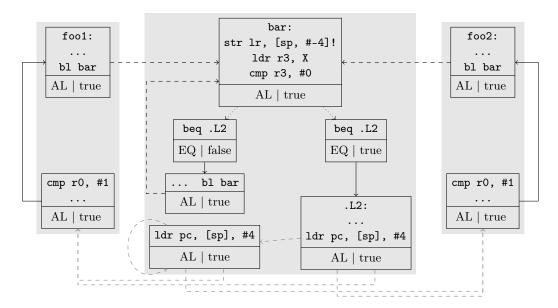

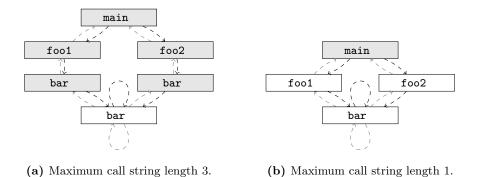

- Chapter 4: The WCC value analysis was developed by the author in collaboration with Jan Körtner, who carried out the majority of the implementation work. The analysis and context graph handling as well as the microarchitectural modeling as presented in this chapter are the work of the author.

• Chapter 5: The WCET analysis approaches for shared buses were entirely designed and developed by the author. They are based on previous work from Chattopadhyay et al. [CRM10], which was later extended in cooperation with the same authors in the publications [KFM+11; KFM+14]. The co-authors of these publications assisted the author in technical discussions, proof-reading and structuring of the publications. Furthermore, the presentation of the analyses in this thesis contains a state which is far more advanced than the one in [KFM+11; KFM+14] and integrates better with the classical microarchitectural analysis. These advances also are original work of the author.

The comparison of arbitration strategies as already published in [KHM+13] was developed by the author of this thesis, based on the platform implementation by Tim Harde.

The WCET analysis for stateful resources considering all possible interleavings of task executions was designed and implemented exclusively by the author and published in [KM14].

• Chapter 6: The optimization opportunities and concepts were developed and formalized by the author. A first version of the implementation was done by Hendrik Borghorst [Bor13] which was later reworked by the author, leading to the publication [KMB14].

## Timing Analysis Concepts

| Conten | $\mathbf{ts}$ |                                                           |    |  |  |

|--------|---------------|-----------------------------------------------------------|----|--|--|

| 2.     | 1 Abs         | Abstract Interpretation                                   |    |  |  |

| 2.     | 2 WC          | ET Analysis for Uninterrupted Single Tasks                | 18 |  |  |

|        | 2.2.1         | Static WCET Analysis                                      | 19 |  |  |

|        | 2.2.2         | Parametric WCET analysis                                  | 21 |  |  |

|        | 2.2.3         | Hybrid WCET analysis                                      | 21 |  |  |

|        | 2.2.4         | Early-Stage WCET analysis                                 | 22 |  |  |

|        | 2.2.5         | Statistical WCET analysis                                 | 22 |  |  |

|        | 2.2.6         | WCET-friendly Hardware Design                             | 23 |  |  |

|        | 2.2.7         | Experiences with Practical Application of WCET Analysis   | 23 |  |  |

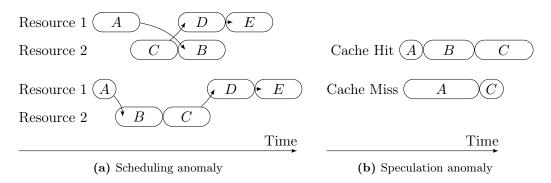

|        | 2.2.8         | Timing Anomalies                                          | 24 |  |  |

|        | 2.2.9         | Compositionality in WCET Analysis                         | 27 |  |  |

| 2.     | 3 Tim         | ing Analysis of Sequential Multi-Task Systems             | 29 |  |  |

|        | 2.3.1         | Accounting for the Timing Behavior of System Calls        | 29 |  |  |

|        | 2.3.2         | Accounting for Task Interaction Impacts on the WCET $$ .  | 30 |  |  |

|        | 2.3.3         | Schedulability of Multi-Task Systems with Given WCETs $.$ | 32 |  |  |

| 2.     | 4 Tim         | ing Analysis of Parallel Multi-Task Systems               | 32 |  |  |

|        | 2.4.1         | Multi-Core Systems                                        | 33 |  |  |

|        | 2.4.2         | Distributed Systems                                       | 34 |  |  |

|        |               |                                                           |    |  |  |

In this chapter we will review the existing literature on WCET analysis and investigate which concepts have already been established in this domain. We start in Section 2.1 with a thorough treatment of abstract interpretation, since this is one very fundamental technique that forms the basis for WCET analysis. In Section 2.2 we examine how this technique and others can be applied in the context of classical WCET analysis. Section 2.3 proceeds with concepts for the timing analysis of multiple tasks on a single processor. Finally, we present existing approaches for the analysis of the WCET of tasks in parallel systems in Section 2.4.

#### 2.1 Abstract Interpretation

Abstract Interpretation (AI) is one of the most well-developed theories for the approximation of states in discrete transition systems. The basic ideas date back to a 1973 publication from Kildall [Kil73] which were later formalized and generalized by Cousot and Cousot [CC77]. The presentation in this thesis is based on the more modern introduction in [ALS+07]. Though AI is applicable to various discrete transitions systems like, e.g., source-code programs, petri nets and Kahn process networks, we base our examples on the approximation of low-level computer system states since these will be the target of WCET analysis.

In general, we can associate a concrete semantics with any computer system. This semantics reflects the transformation of all memory cells in the system by operations carried out by the computational circuits. Since all currently relevant computer systems are working in clocked operation, we can define these transformations on discrete time steps. Therefore, if  $\tilde{L}$  is the set of all possible memory cell assignments including all registers, the program counter, current instruction and otherwise stored values, a single cycle of a computer system's operation can be deterministically described by a concrete semantics function  $[]_{conc}: \tilde{L} \mapsto \tilde{L}$ . Since all relevant computer systems are also working on a well-defined instruction set, concrete states are always generated by programs.

**Definition 1.** A program  $X = (i_0, i_1, ..., i_n)$  is a sequence of instructions  $i \in I$  from a global instruction set I with start instruction  $i_0$  and a set of terminal instructions  $I_t$ . An execution of X is a trace of concrete system states  $(\tilde{l}_0, \tilde{l}_1, ..., \tilde{l}_m)$  such that

- $\tilde{l}_0$  encodes X in its memory content and executes  $i_0$ , and

- $\forall i \in \{1, m\} : \tilde{l}_i = [\![\tilde{l}_{i-1}]\!]_{conc}, and$

- $pc(\tilde{l}_m) \in I_t$ .

where  $pc: \tilde{L} \to I$  extracts the value of the program counter from a concrete state.

An ideal analysis would determine the execution trace for every possible initial system state  $\tilde{l}_0$ . The length of the longest of these traces would be the WCET of the program under analysis. Obviously, a naive attempt to collect all of these traces and return them as the analysis result will fail, since

- a) there may be traces of infinite length corresponding to non-terminating programs and

- b) modeling the *whole* state of the system under analysis and maintaining huge numbers of these states during the analysis is practically infeasible.

To be able to reason about program executions in a structured way, the notion of a control-flow graph is used.

**Definition 2.** A basic block  $v = (i_0^v, ..., i_k^v)$  of a program X is a maximal subsequence of X, such that for all  $j \in \{1, ..., k\}$  and  $\tilde{l}, \tilde{l}' \in \tilde{L}$

$$\left(pc(\tilde{l}) = i_j^v \wedge [\tilde{l}']_{conc} = \tilde{l}\right) \Longrightarrow \left(pc(\tilde{l}') = i_j^v \vee pc(\tilde{l}') = i_{j-1}^v\right). \tag{2.1}$$

A Control Flow Graph (CFG)  $(V, E, v_0)$  of a program X, with V being the set of basic blocks of X and  $E \subset V \times V$  being a set of directed edges which model every possible transfer of control within the program. The entry point of the program is given by node  $v_0$ .

A path P in a CFG from  $v_s \in V$  to  $v_e \in V$  is a non-empty sequence of nodes  $P = (v_s, \ldots, v_e)$  such that for any two adjacent  $v_i$  and  $v_{i+1}$  in P,  $(v_i, v_{i+1}) \in E$  holds. If a path from  $v_s \in V$  to  $v_e \in V$  exists, we call  $v_e$  reachable from  $v_s$  which is expressed as  $v_s \leadsto v_e$ , else  $v_e$  is unreachable from  $v_s$  written as  $v_s \leadsto v_e$ . The set of all paths from  $v_s$  to  $v_e$  is called  $P_{[v_s,v_e]}$ . For any node  $v \in V$ ,  $\delta^+(v) = \{w \mid (v,w) \in E\}$  and  $\delta^-(v) = \{w \mid (w,v) \in E\}$  are the successors and predecessors of v.

The connection between traces of concrete states and the CFG is easily made, since each  $\tilde{l} \in \tilde{L}$  holds a concrete value of the *Program Counter* (PC) register of the underlying architecture, which points to an instruction  $i_{\tilde{l}} \in I$ . Thus, if each  $\tilde{l}_j$  of a trace is mapped to the node  $v \in V$  with  $i_{\tilde{l}_j} \in v$  the trace is transformed to a CFG path.

A path is called *feasible*, if there is a concrete trace which is mapped to this path. Infeasible paths may exist in a CFG due to dependencies between control flow branches, which are not reflected in the graph structure. As an example, if two branches  $b_1$  and  $b_2$  have the same branch condition and the value of the condition remains unmodified between  $b_1$  and  $b_2$ , then either both branches are taken or none. The CFG, in contrast, may also contain an infeasible path in which  $b_1$  is taken whereas  $b_2$  is not. A *cycle* at  $v \in V$  is a path  $(v, \ldots, v)$ . A path which contains no cycle is called *acyclic*. The set of all paths  $P_{[v_s, v_e]}$  can be restricted to feasible  $(P_{[v_s, v_e]}^{\text{feasible}})$  or acyclic paths  $(P_{[v_s, v_e]}^{\text{acyclic}})$ .

To deal with issue a) from above, the collecting semantics  $[\![]]_{coll}: 2^{\tilde{L}} \times V \mapsto 2^{\tilde{L}}$  is defined as taking a set of concrete states, executing the instructions from the given CFG node in those states for all possible inputs and returning the resulting end states. We can trivially extend the collecting semantics to paths  $p = (v_1, v_2, \dots v_n)$  by setting  $[\![s]\!](p) = [\![\dots]\!][\![s]\!](v_1)]\!](v_2)\dots]\!](v_n)$ . We are then searching for the state set  $s_v^{coll} = \bigcup_{p \in P_{[v_0,v]}, \tilde{l}_0 \in \tilde{L}}[\![\tilde{l}_0]\!](p)$  for every node  $v \in V$ . If  $\tilde{L}$  has infinite cardinality, this result may still be infinitely big. To overcome this and the issue b) mentioned above, AI further changes from the collecting semantics  $[\![]\!]_{coll}$  to an abstract semantics  $[\![]\!]_{abs}: \mathbb{L} \times V \mapsto \mathbb{L}$  which is defined on abstract system states  $\mathbb{L}$ . To be useful, the abstract semantics must overapproximate the collecting one, which is expressed by the notion of a Galois connection.

**Definition 3.** A Galois connection  $(\alpha, \gamma)$  is a pair of functions  $\alpha : P \mapsto Q$  and  $\gamma : Q \mapsto P$  for two sets with partial orders  $(P, \leq)$  and  $(Q, \sqsubseteq)$  such that

$$\forall x \in P, y \in Q : \alpha(x) \subseteq y \Leftrightarrow x \le \gamma(y)$$

(2.2)

For our concrete example, this means  $(P, \leq) = (2^{\tilde{L}}, \subseteq)$  and  $(Q, \equiv) = (\mathbb{L}, \equiv)$ , where  $x \equiv y$  if and only if  $\gamma(x) \subseteq \gamma(y)$ . I.e., an abstract state x is "bigger" than y if and

Figure 2.1: The Galois connection between concrete and abstract semantics.

only if it "contains" a superset of the concrete states which are contained in y. This is a general necessity in a Galois connection, where we also have the property, that  $x \leq \gamma \circ \alpha(x)$ , e.g., the re-concretization of an abstraction of x always contains x. The general idea is visualized in Figure 2.1. With the abstraction function  $\alpha$ , we can map the initial system states into the abstract domain  $\mathbb{L}$ , where we conduct our analyses to compute abstract results  $l_v^{out}$ . After the analysis is finished the Galois condition ensures that  $\gamma(l_v^{out}) \supseteq s_v^{coll}$ , i.e., every reachable concrete state is covered in the result. Since we are computing an overapproximation, potentially also other states which are not reachable in any concrete execution are covered.

For the analysis to be efficiently possible, the abstract domain  $\mathbb L$  must be a semi-lattice.

**Definition 4.** A semi-lattice  $(\mathbb{L}, \sqcup)$  is a set  $\mathbb{L}$  with a meet operator  $\sqcup : \mathbb{L} \to \mathbb{L}$ , which is required to be

- $idempotent: \forall l \in \mathbb{L}: l \sqcup l = l$ ,

- commutative:  $\forall l, m \in \mathbb{L} : l \sqcup m = m \sqcup l$  and

- associative:  $\forall l, m, n \in \mathbb{L} : l \sqcup (m \sqcup n) = (l \sqcup m) \sqcup n$ .

The meet operator induces a partial order  $\sqsubseteq$  on  $\mathbb{L}$ , which is defined by

$$\forall l, m \in \mathbb{L} : l \subseteq m \Leftrightarrow l \sqcup m = m \tag{2.3}$$

In a semi-lattice  $(\mathbb{L}, \sqcup)$ , also a biggest element  $\top = \sqcup \mathbb{L}$  exists, with  $\forall l \in \mathbb{L} : l \sqcup \top = \top$  or equivalently  $\forall l \in \mathbb{L} : l \sqsubseteq \top$ . This element is usually named "top". Additionally, a smallest element  $\bot \in \mathbb{L}$  ("bottom") may exist, with  $\forall m \in \mathbb{L} : \bot \sqcup l = l$ .

The height of a lattice is one less than the length of the longest sequence  $(l_1, l_2, ..., l_n)$  of  $l_i \in \mathbb{L}$  such that  $\forall i : l_i \subseteq l_{i+1}$ .

**Definition 5.** A monotonic Data-Flow Analysis (DFA) framework  $((\mathbb{L}, \sqcup), F)$  consists of a

- $semi-lattice (\mathbb{L}, \sqcup) and$

- a set F containing functions  $f: \mathbb{L} \to \mathbb{L}$ , where

- 1. every f is monotonic in  $\subseteq$ , i.e.,  $\forall l, m \in \mathbb{L} : l \subseteq m \implies f(l) \subseteq f(m)$ ,

- 2. the identity function id with  $\forall l \in \mathbb{L} : id(l) = l$  is contained in F and

3. F is closed under function composition, i.e.,  $\forall f, g \in F : f \circ g \in F$ .

A DFA framework is called distributive iff

$$\forall f \in F, l, m \in \mathbb{L} : f(l \sqcup m) = f(l) \sqcup f(m) \tag{2.4}$$

The weaker form of this condition  $f(l \sqcup m) \subseteq f(l) \sqcup f(m)$  is already true also for non-distributive DFA frameworks.

**Definition 6.** An instance of a DFA framework  $((\mathbb{L},\sqcup),F)$  is a tuple  $((V,E),v_0,l_0)$ , where (V,E) is a control-flow graph of the program to analyze,  $v_0$  is the node where the control flow enters the program and  $l_0 \in \mathbb{L}$  is the initial data-flow information for the start node and every node  $v \in V$  has an associated transfer function  $f_v \in F$ . A solution for an instance is a set of data-flow items  $l_v^{out}$  for all  $v \in V$  such that the reachable concrete states  $s_v^{coll}$  are covered, i.e.,  $\gamma(l_v^{out}) \supseteq s_v^{coll}$ .

The transfer functions are just invocations of the abstract semantics, i.e.  $f_v = []_{abs}(v)$  and similar to it, we can extend the transfer function to CFG paths. By following all feasible paths through the program's control flow graph given by a DFA framework instance, we can define an *ideal* solution

$$l_v^{out, \text{IDEAL}} = \bigsqcup_{p \in P_{[v_0, v]}^{\text{feasible}}} f_p(l_0)$$

(2.5)

Since the identification of feasible paths in impossible in general, we can relax this to the *Meet Over All Paths* (MOP) solution, which considers all paths in the CFG

$$l_v^{out,\text{MOP}} = \bigsqcup_{p \in P_{[v_0,v]}} f_p(l_0)$$

(2.6)

The MOP solution is still not computable, since there may be infinitely many paths due to the existence of loops in the CFG as already discussed. Therefore as the last coarsening step, we revert to the *Minimum Fixed Point* (MFP) solution which is the fixed point of Equation 2.7.

$$l_v^{out,\text{MFP}} = \begin{cases} f_v(l_0) & \text{if } v = v_0 \\ f_v\left(\bigsqcup_{(u,v)\in E} l_u^{out,\text{MFP}}\right) & \text{else} \end{cases}$$

(2.7)

This solution avoids the computation of all paths by only propagating the states via the edges of the CFG until a fixed point is reached. During this procedure all finite paths are visited implicitly. From the fixed point definition we also know, that for all infinite paths to v the generated data-flow information is covered by  $l_v^{out, \text{MFP}}$ . Further details on why the precision relation  $l_v^{out, \text{MFP}} \supseteq l_v^{out, \text{MOP}} \supseteq l_v^{out, \text{IDEAL}}$  is true for all  $v \in V$  can be found in [ALS+07, Chapter 9.3].

For monotonic frameworks, an MFP solution always exists according to the Knaster-Tarski-Fixed-Point Theorem [Tar55]. In general, the MOP solution is more precise than the MFP one, since in the MFP case we apply the meet operator

#### Algorithm 1 The generic data-flow analysis work-list algorithm.

```

1: function WorkListAlgorithm(((\mathbb{L}, \subseteq), F), ((V, E), v_0, l_0))

worklist \leftarrow v_0

2:

for v \in V do

\triangleright Initialization of the l_v^{in}/l_v^{out} ...

3:

if v = v_0 then

4:

l_v^{in} \leftarrow l_0, l_v^{out} \leftarrow \bot else l_v^{in} \leftarrow \bot, l_v^{out} \leftarrow \bot

\triangleright ... for the start node ...

5:

6:

\triangleright ... and for all other nodes.

7:

while worklist \neq \emptyset do

▶ Loop until a fixed point was found

8:

v \leftarrow \text{pop}(\text{worklist})

9:

l_v^{in} \leftarrow \bigsqcup_{(u,v) \in E} l_u^{out}

l_v^{tmp} \leftarrow f_v(l_v^{in})

if l_v^{out} \neq l_v^{tmp} then

l_v^{out} \leftarrow l_v^{tmp}

10:

\triangleright Apply transfer function of node v

11:

\triangleright If there were changes at node v ...

12:

13:

for (v, w) \in E do

14:

push(worklist, w)

15:

return \{v \to l_v^{in} \mid v \in V\}

16:

```

earlier than in the MOP case, namely after each node instead of only after each path. For distributive frameworks this does not make a difference (see Equation 2.4), therefore the MFP solution is equal to the MOP solution for distributive frameworks ("Interprocedural Coincidence Theorem" [KS92]). For computing the MFP solution, the work-list algorithm is a standard approach as shown in Algorithm 1.

The data-flow information is initialized in lines 3-7 and then propagated through the graph in lines 8-15. The nodes at which the data-flow information has not yet converged are kept in a work-list which is processed until all state information has converged. As mentioned, this convergence relies on the monotonicity of the height of the underlying lattice. For finite-height lattices, the convergence is guaranteed, since any data-flow item either reaches a fixed point other than  $\top$ , or reaches  $\top$  in a finite number of steps which is a forced fixed point due to the monotonicity of the transfer functions. To speed up the convergence of the data-flow items we can sort the work list in topological order, ignoring back-edges in the CFG.

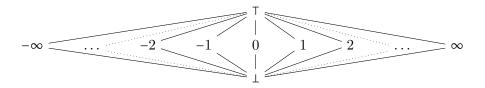

As an example for a lattice, consider the problem of determining whether a single register has a constant value at the individual CFG nodes. The Hasse diagram of the lattice for this problem is shown in Figure 2.2. It has a finite height of 2, though it has an infinite number of elements. The bottom element  $\bot$  denotes the state "register was not initialized", the top state  $\top$  means "register does not hold a constant value" and the middle row of elements represents actual constants. Whenever a block v loads a constant value into the register,  $l_v^{out}$  is set to this value. If multiple constants are merged in the meet operation,  $l_v^{in}$  is set to  $\top$  in Algorithm 1. Further examples and an overview of possible lattices for program analysis can be found in [Cou01].

Figure 2.2: The lattice of integer constants.

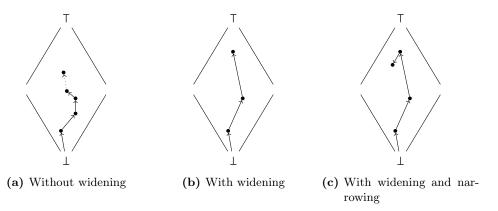

Since the convergence of Algorithm 1 is not guaranteed for lattices with infinite height, such as intervals on integer numbers, *widening* is used to enforce the termination of the abstract interpretation in such lattices.

**Definition 7.** A widening operator  $\Delta$  is a unary function on  $\mathbb{L}$ , such that  $\forall l \in \mathbb{L} : l \subseteq \Delta(l)$  and for any sequence  $l_1, l_2, \ldots$  with  $\forall i > 1 : l_i \supset \Delta(l_{i-1})$  the top element is reached in a finite number of steps, i.e.,  $l_n = \top$  for some  $n \in \mathbb{N}$ .

With a widening installed, line 11 in Algorithm 1 becomes

$$l_v^{tmp} \leftarrow \Delta \left( f_v \left( l_v^{in} \right) \right)$$

After the fixed point was found, it is possible to refine the results again by letting the main loop of Algorithm 1 iterate again for a user-defined number of times with the original definition of  $l_v^{tmp}$ , i.e., without the widening. This process may remove some of the overestimation induced by the widening and is called narrowing. In Figure 2.3 an example is given, how widening and narrowing affects the generated results. The figures show the Hasse diagram of the lattice and the evolution of a single data-flow value (one  $l_v^{out}$  for a fixed node v) during the runtime of the fixed point determination. Every arc corresponds to one iteration of the main loop from Algorithm 1 for v. The widening skips over many intermediate values by artificially coarsening the results of the individual steps. This speeds up the convergence (reduced number of arcs) but also leads a more imprecise result (higher in the Hasse diagram). The narrowing is able to re-gain some precision by applying the unmodified transfer functions to the fixed point values. It can lead to results which are at best as good as in the case without widening, but usually they are worse.

To further refine the results of the data-flow analysis, path-awareness can be introduced as shown in [HT98], which inflates the analysis lattice by multiplying it with a lattice that represents some of the edges that were visited during the generation of a data-flow information item. If that is done, data-flow items with different path expressions are not merged, which potentially increases the precision if the original lattice was not distributive. In addition, path-awareness can be used to rule out infeasible paths [NKJ10] if the edges in the path have contradictory guard conditions, thus moving the fixed-point result a step closer to the IDEAL solution sketched above. All of this comes at the price of increased analysis duration, since the size of the underlying lattice is multiplied by the number of possible edge

**Figure 2.3:** Convergence behavior in a lattice. Solid and dotted arcs represent one or indefinitely many applications of the transfer function, respectively.

strings. Therefore, [NKJ10] try to limit the edge strings to relevant edges only, heuristically. Another approach to control the complexity of the path-awareness is to gradually increase the allowed length of the path expressions during the analysis as shown in [DDY06], where the authors use this method to analyze large real-world benchmarks. As a last option, [BSI+08] separate the detection of infeasible paths from the data-flow analysis itself and re-structure the program such that infeasible paths are avoided also in a non-path-aware analysis.

With the systematical description of a DFA framework coined above, it should not be surprising that DFA implementations for concrete problems can easily be generated from compact lattice and transfer function descriptions [SSB09], even for path-aware DFAs [HMM12].

### 2.2 WCET Analysis for Uninterrupted Single Tasks

In this section we will review the existing approaches to the determination of WCET estimates for a single program running without interruption on a single-core computer with no other active hardware components which could interfere with the program under analysis. This is the most basic of all WCET analysis scenarios, but it already offers a plethora of pitfalls and problems to solve [WEE+08]. In general, the challenges that WCET analysis is facing in this scenario fall into one of the following categories:

• Unpredictable hardware components: The WCET analysis has to follow all execution paths of the hardware to find the path with maximum execution time. Abstract interpretation can relieve this problem to some limited extent, but strong abstractions on the hardware state also lose much precision. Therefore, hardware features which increase the state space of the pipeline or memory hierarchy such as caches, superscalar and out-of-order execution,

Figure 2.4: Structure of most static WCET analyzers.

fetch and commit queues and speculative execution complicate the WCET analysis [WGR+09].

• Unpredictable software structure: Usage of runtime-dynamic software constructs like function pointers, virtual inheritance and even dynamic memory allocation is hard to analyze statically. These can be circumvented to some extent by coding conventions such as MISRA-C [MIS13] which prohibit the usage of these features. Nevertheless even predictably-designed software exhibits an iteration structure of loops and recursions which may be not analyzable statically. Here, the user has to intervene in the worst case and needs to give hints to the WCET analyzer [KKP+11].

The following subsections will introduce the important branches of single-task WCET analysis, review real-life examples and case studies of their application and finally finish with an introduction to timing anomalies and compositionality, two concepts which are central to WCET analysis and frequently used in the following sections.

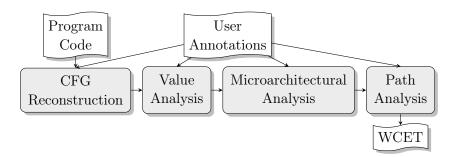

#### 2.2.1 Static WCET Analysis

Static WCET analysis analyzes a program without executing any part of it, solely based on abstract models of the hardware and program semantics. Therefore, it provides stronger safety and coverage guarantees than measurement-based methods. The usual approach is to separate the analysis into multiple steps as shown in Figure 2.4.

A program, which, depending on the analyzer, may be given in binary or source-code form, is first fed into the *control-flow graph reconstruction* which extracts an interprocedural control-flow graph that reflects all possible transitions of control flow among instructions from the given program. In case of non-analyzable control-flow transitions, such as function pointers, the user might be required to specify their targets manually. After this step, the *value analysis* computes safe approximations of the register or variable values by means of AI on the generated CFG. The user can manually refine these results if he is not satisfied with their precision. The *microar-chitectural analysis* uses the CFG and the value results to provide overestimates of

the possible hardware states at each CFG node, again usually by means of AI. The user might have to specify machine details like the used clock frequency and the memory hierarchy specification for this step. Finally, the *path analysis* computes the WCET result. To achieve this, it must know upper bounds on the execution frequency of all cyclic paths, i.e., loops and recursions. For simple cases, the value analysis will deliver these bounds, whereas for complex loops the user has to provide a bound.

The prime example of an implementation of this scheme is the AIT WCET analyzer from AbsInt GmbH [FH04], which is the most well-known and industrially-used WCET analyzer available. The analysis that was implemented for this thesis inside the WCC [FL10] also follows this line of research, as well as other industrial and academic WCET projects like BOUND-T [Tid04], the Open Timing Analysis Platform (OTAP) [HPP11], the OTAWA framework [Tea14], the CALCWCET167 tool [Kir12], SWEET [MRT14], CHRONOS [LLM+07] and TUBOUND [PSK08]. Apart from AIT, all of these tools were written mainly for research purposes and have experimental or simplified versions of individual analysis stages. Most importantly, only AIT includes an abstract processor model also for non-trivial target processors in the microarchitectural analysis. In Chapter 4 we will look at the individual analysis stages in more detail, where we also show their realization inside the WCC.

The analysis structure sketched in Figure 2.4 can be regarded as the most promising approach to WCET analysis. Nevertheless, it is not the only one. Modelchecking has proven to be effective in the analysis of distributed real-time systems [AD90; BY04; FKP+07]. There also exist proposals to determine the WCET using model-checkers, which requires the whole architecture and the program under analysis to be modeled as a transition system amenable to classical model-checking theory. The main drawback of early approaches was the fact, that a dedicated model has to be created which reflects the timing of the program under analysis [CCM97]. Any error done in the manual modeling invalidates the results. More recent approaches incorporate program and hardware state into the model, e.g., using a generic model-checker like UPPAAL to solve the WCET problem [BC11]. The usage of a generic model-checker opens up the possibility to model arbitrarily complex systems. Unfortunately, due to the same reason, these approaches also lack the capabilities to form controlled abstractions of the resulting state space which leads to poor analysis times when compared to abstract interpretation-based designs [Wil04]. In experimental results from Gustavsson [GEL+10] runtimes of more than 30 hours are reported even for drastically simplified architectures. Similarly, the path analysis speed is far inferior with model checking than with classical methods based on Integer Linear Programs (ILPs) [HS09].

A third, but now outdated approach is the integration of microarchitectural analysis and path analysis into one single ILP. This was only attempted for simplified architectures, where only a cache was modeled, and already there major problems with the scalability of this method were found [LMW95; LMW96].

#### 2.2.2 Parametric WCET analysis

One problem of the "classical" approach to WCET analysis as shown in the last subsection is, that the result is a single numeric value. For software which shows significant variation in its runtime, it would be better if the WCET analysis yielded a formula which describes the WCET depending on the program's input parameter values. This concept is called parametric WCET analysis. If the variables in the WCET formula are input values, we specifically call it input-parametric. According to an industrial case study from Gustafsson and Ermedahl [GE07] the lack of parametric WCET analysis tools is one major shortcoming of present WCET analyzers.

The main problem for input-parametric WCET analysis is the path analysis stage, which now must produce a WCET formula describing the longest path through the CFG depending on input values which may trigger different behaviors of loop and condition structures in the program under analysis. Methods for constructing such formulas are stepwise CFG reductions [AAN11], algebraic simplification of weighted path expressions [HPP12], solving symbolic ILP problems [AHL+08; BL08], custom graph-flow algorithms [BEL11] and symbolic evaluation [Bli02].

A less complex but also more restricted approach is the identification of execution scenarios prior to WCET analysis. These are often present in the software structure if the code is able to run in different input-defined modes. For each identified scenario a separate WCET analysis can be conducted with user annotations that force the analyzer to limit the examined program paths to those of the particular scenario [LPW09; MA11; HKB+14]. The generated WCET formula thus only assigns a single numeric WCET value to each scenario, which is identified by the inputs that trigger this scenario.

Apart from input-parametric WCET analysis, there have recently also been efforts to establish architecture-parametric WCET analysis [RD14]. In the latter case, the WCET formula is a function of architectural properties of the system under analysis. This mainly affects the microarchitectural analysis, which must now generate results for all possible target hardware configurations. Although architecture-parametric WCETs would be useful, input-parametric WCETs are a more urgent problem in practice [GE07].

#### 2.2.3 Hybrid WCET analysis

As a counterpart to static WCET analysis, dynamic WCET analysis refers to endto-end measurements of the program runtime on the actual hardware. These will not be safe unless all input parameter and initial system configuration combinations were exercised, which is infeasible for any real-world system.

Thus, to re-gain some confidence in the results supplied by dynamic WCET analysis, *hybrid WCET analysis* was proposed. It replaces the value and microarchitectural analysis from Figure 2.4 with a measurement of the runtime of each CFG node and then continues with the known path analysis methods from static WCET

analysis to derive the WCET estimate. Since the measured CFG node runtimes are not guaranteed to be safe, this method is only suited for soft real-time tasks, where precision of the estimate is the main concern. An industrial analyzer which uses this technique is the *RapiTime* tool from Rapita Ltd. [Ltd14]. To increase the confidence in this method, test input generation heuristics like the *Balanced Path Generation* [BZT+11] have been proposed.

#### 2.2.4 Early-Stage WCET analysis

Typically, WCET analysis can only be applied after the complete binary code of the program to be analyzed is available and the hardware platform on which it should run is known. This is needed for the WCET analysis to be safe, since all program execution paths on the platform must be considered hence both the program and the platform must be known. Early-stage WCET analysis abandons safeness in favor of getting early results, even for models of the systems which are not yet available in binary form. For these models, a safe estimation is hardly possible, instead an efficient, early feedback on the achievable WCET is requested. For this purpose, mostly regression with linear models is used [GAE+09], which are trained with WCET values of high-level programs [AEL+11]. The results are not safe, nor is there any known bound on the maximum deviation from the true WCET, but empirical results indicate that early-stage WCETs have a deviation of less than 20% compared to the final, safe WCET values.

#### 2.2.5 Statistical WCET analysis

Since any computing hardware has some defined mean time before failure, statistical WCET analysis is an attempt to compute a probability distribution of execution times of a task on a given platform. If the probability for a violation of the task's deadline is at least as small as the probability of a hardware failure, the remaining failure probability can be acceptable [Höf12; KVA+13]. Still, many assumptions have to be verified before applying this concept, like the statistical independence of the probability distributions of software and hardware events [SLL+11]. In practice, proving this independence will be challenging and possibly lead to unsafe results if invalid assumptions are made.

A relatively new approach to this problem is *Probabilistic Timing Analysis* (*PTA*), which tries to justify these independence claims by requiring a hardware where everything is randomized as far as possible, from the memory layout over microarchitectural aspects to the cache placement and replacement policies [CQV+13]. However, a recent publication [Rei14] shows that the handling of randomized caches in current PTA approaches is unsafe, and that deterministic replacement policies like LRU perform consistently better, even in the context of PTA. It is also shown that statistical independence of microarchitectural event distributions, which is the basis of PTA, was often wrongly assumed [Rei14]. Therefore, this analysis branch can only be considered highly experimental in its current state.

#### 2.2.6 WCET-friendly Hardware Design

Even mainstream processor development has acknowledged the need for more predictable hardware, though only to a limited extent. As an example, the ARM Cortex-R series of processors [ARM14a] features local scratchpads for each core and a time-predictable interrupt handling. Nevertheless, it still contains a deep superscalar pipeline with speculative execution and instruction pre-fetching. Though these are not necessarily features which hamper the "observed predictability", i.e., the timing variation between multiple independent measurement runs, they still complicate a static WCET analysis by increasing the hardware state space considerably. The Infineon AURIX series [Inf14] shows similar properties from the analysis point of view, though with a shallower pipeline and a higher focus on safety and security. Lastly, the popular Kalray MPPA 256 manycore [KAL14] is an example for how power-awareness can also increase the predictability. To achieve power-efficiency while maintaining high performance it implements a VLIW architecture which is not only more power-efficient than dynamic out-of-order processors but also fundamentally easier to analyze.

In contrast to that, there exist multiple academic proposals for more predictable hardware. The most extreme of these are proposals to make the hardware capable of running in a *worst-case mode* [ORM+09] or to design hardware with constant-execution-time instructions such as the Java-Optimized Processor [SPP+10] or the PRET machine [LRB+12].

Other ideas include the instantiation of a dedicated DRAM-refresh software task to replace the unpredictable hardware DRAM refresh [BM11] and the adaption of the cache hierarchy [HPS12] or the load-store-buffer [MR12] to the needs of WCET analysis.

## 2.2.7 Experiences with Practical Application of WCET Analysis

Multiple case studies have been conducted on the usability of static WCET analysis in practice. These studies indicate that the tools are usable by non-experts [TSH+03] and that a maximum overestimation between 4% and 33% is achievable [GE07; CSB+10]. Compared to "traditional" methods which measure the runtime and add a safety margin, improvements of approximately 10% were observed [TSH+03]. Since static analyses must be able to safely bound all program loops, the user may have to provide such bounds if they cannot be found automatically. This is an issue especially for loops in operating system kernels, which are often data-dependent. The manual bounding of such loops is time-consuming and often requires assistance from the original developers of the respective binary code [GE07].

For tools which operate on the source-level, like SWEET, also the development toolchain poses problems since they need to integrate with it to find all source files which might be written in differing, non-compatible source-language dialects [LES+13]. Even worse, the source code might be missing altogether because a

**Figure 2.5:** The execution paths of a program on a timing-anomalous system depicted by transitions between hardware states.

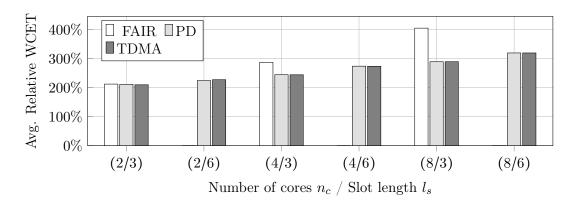

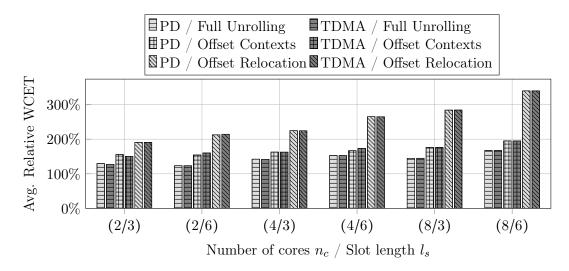

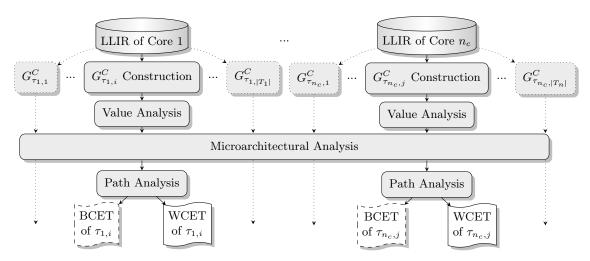

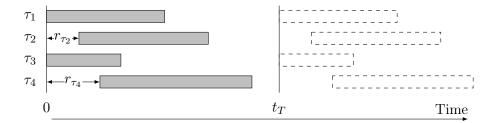

particular component is supplied by a subcontractor [LES+13]. This provides strong arguments in favor of binary-level analysis, where these problems do not exist.